Multi-Core and Hyper-Threading Technology 7

7-3

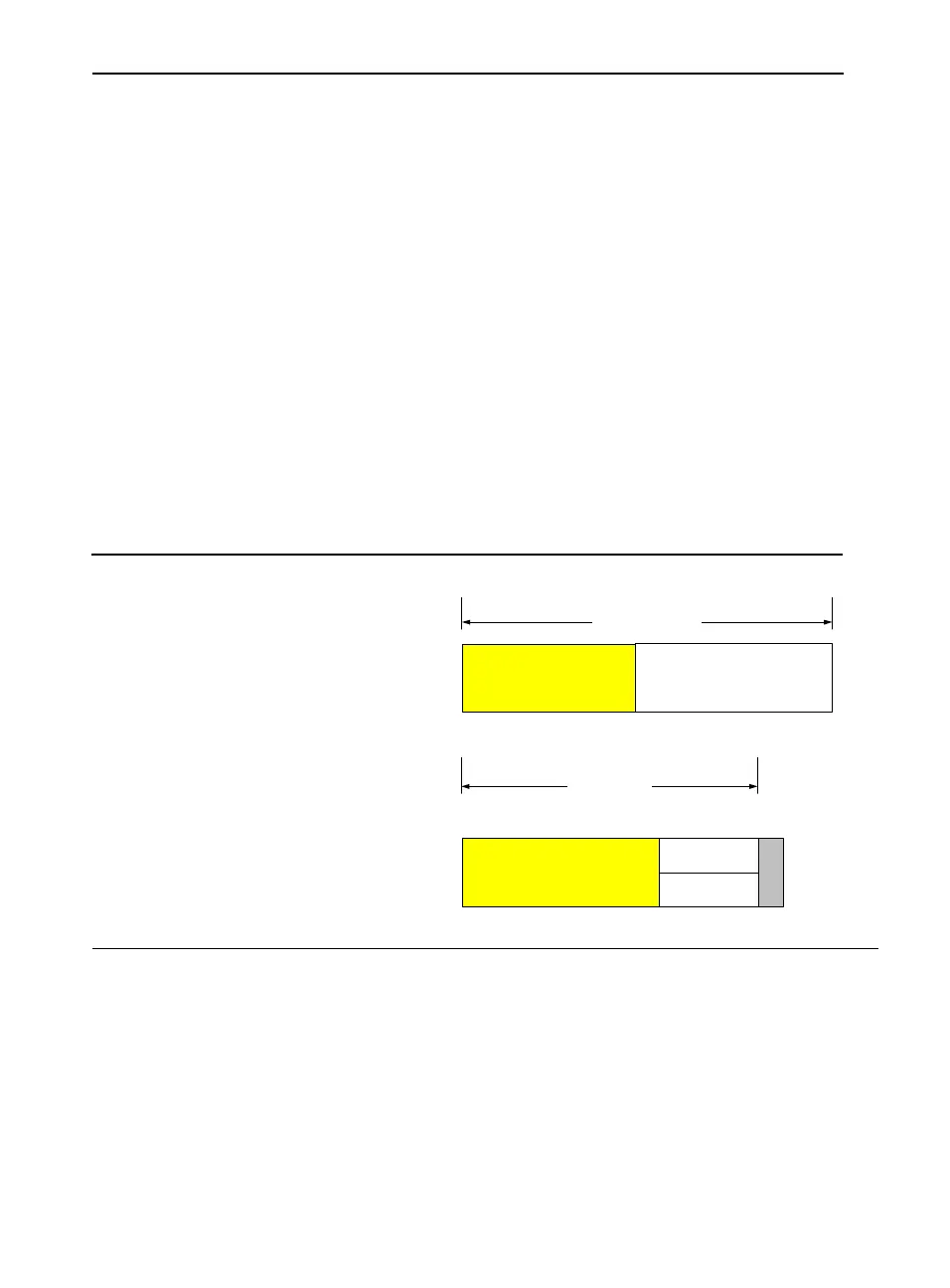

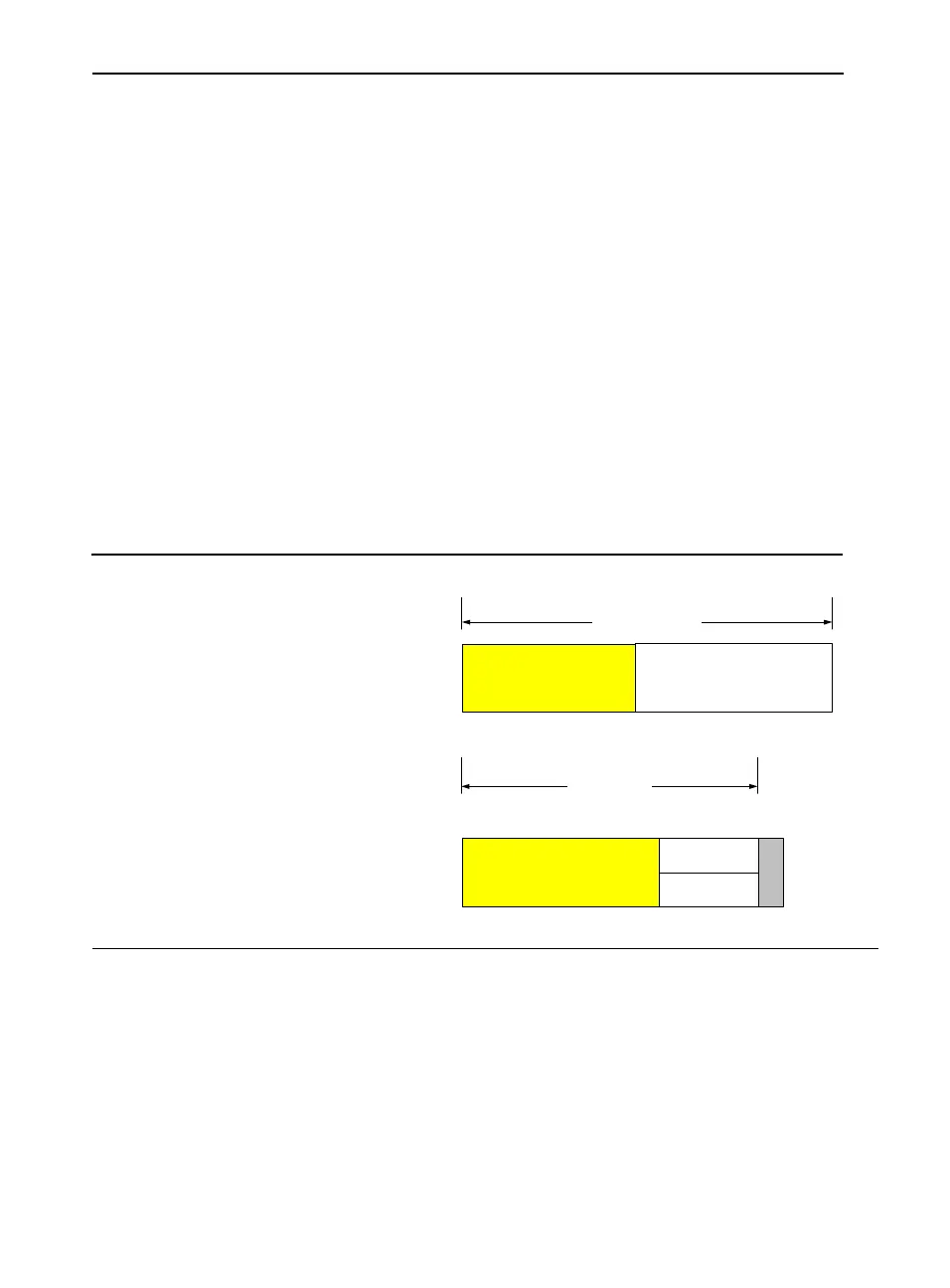

Figure 7-1 illustrates how performance gains can be realized for any

workload according to Amdahl’s law. The bar in Figure 7-1 represents

an individual task unit or the collective workload of an entire

application.

In general, the speed-up of running multiple threads on an MP systems

with N physical processors, over single-threaded execution, can be

expressed as:

where P is the fraction of workload that can be parallelized, and O

represents the overhead of multithreading and may vary between

different operating systems. In this case, performance gain is the inverse

of the relative response.

Figure 7-1 Amdahl’s Law and MP Speed-up

RelativeResponse

Tsequential

Tparallel

-------------------------------= 1 P–

P

N

---- O++

⎝⎠

⎛⎞

=

1-P

P

Tsequential

1-P

P/2

Tparallel

P/2

Single Thread

Multi-Thread on MP

Overhead

Loading...

Loading...