Optimizing for SIMD Integer Applications 4

4-15

If all of the operands in a register are being replaced by a series of

pinsrw instructions, it can be useful to clear the content and break the

dependence chain by either using the

pxor instruction or loading the

register. See the “Clearing Registers” section in Chapter 2.

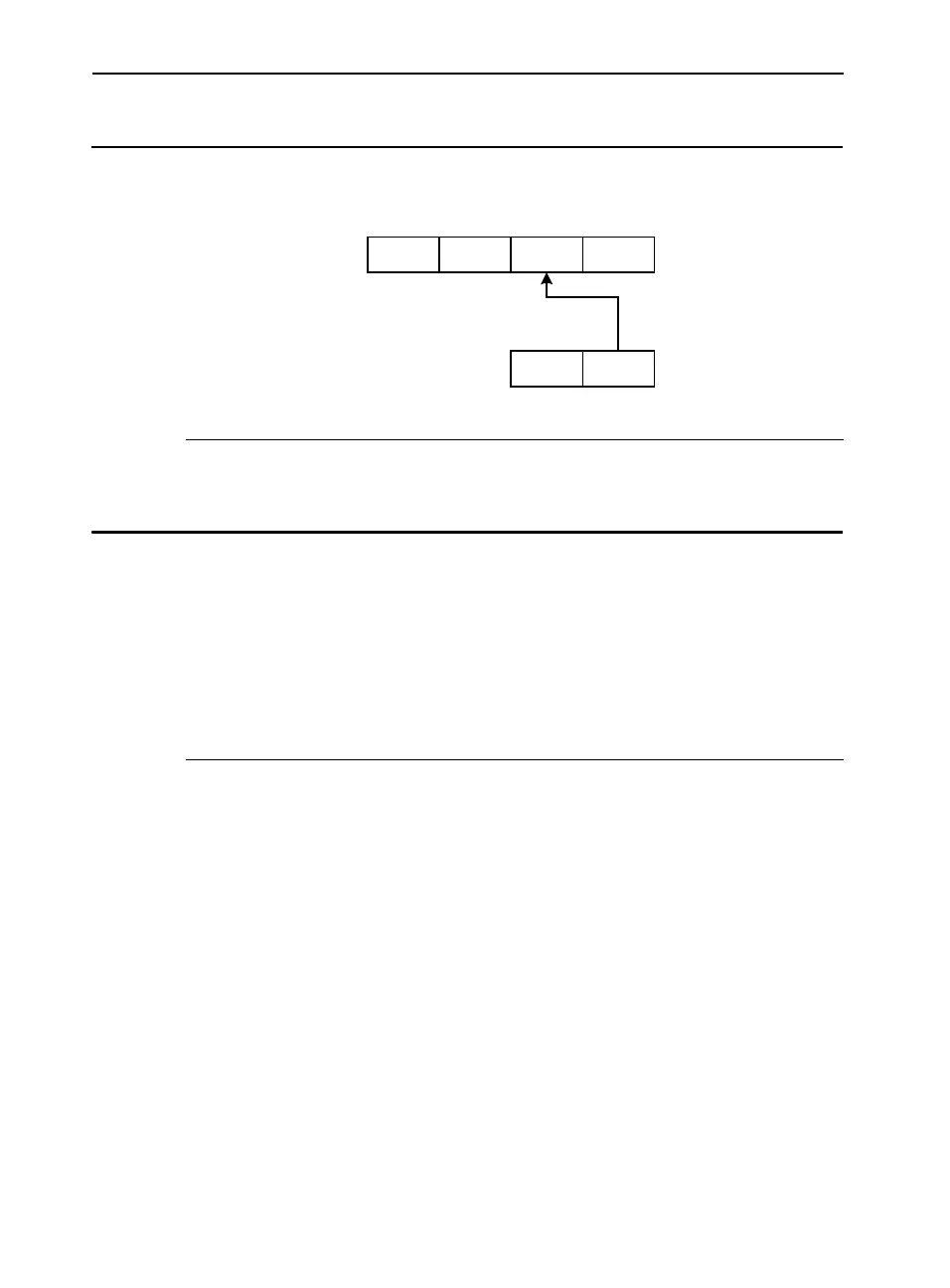

Figure 4-6 pinsrw Instruction

Example 4-8 pinsrw Instruction Code

; Input:

; edx pointer to source value

; Output:

; mm0 register with new 16-bit value inserted

;

mov eax, [edx]

pinsrw mm0, eax, 1

OM15164

Y2

MM

R32

31 0

31 063

X4 X3 Y1 X1

Y1

Loading...

Loading...