IA-32 Intel® Architecture Optimization

E-8

The following formula shows the relationship among the parameters:

It can be seen from this relationship that the iteration latency is equal to

the computation latency, which means the memory accesses are

executed in background and their latencies are completely hidden.

Compute Bound (Case: T

l

+ T

b

> T

c

> T

b

)

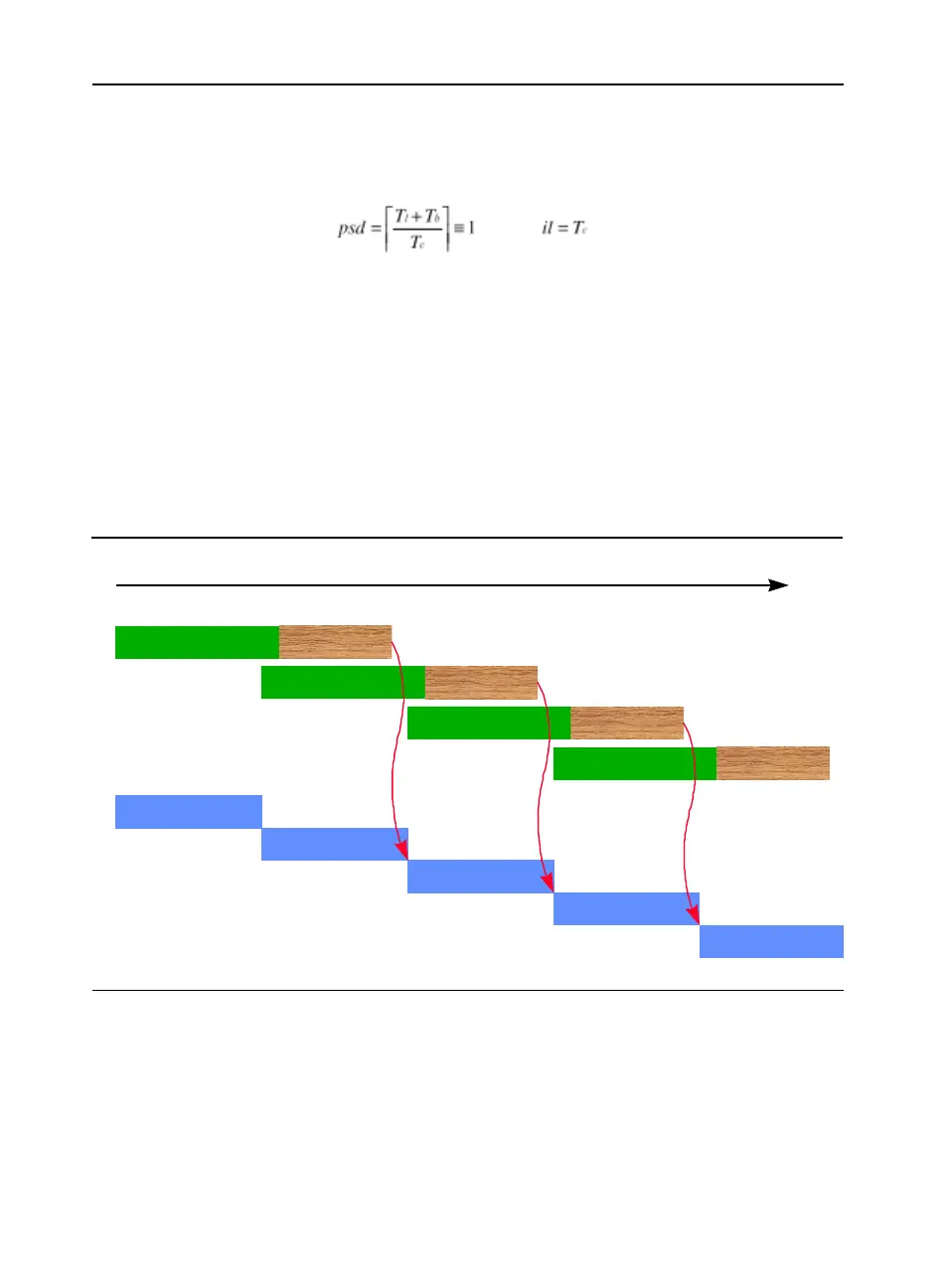

Now consider the next case by first examining Figure E-4.

Figure E-4 Another Compute Bound Execution Pipeline

Execution cycles

Front-Side Bus

Execution pipeline

i

i+1

i+2

i+3

i

i+1

i+2

i+3

T

c

T

c

T

c

T

c

T

l

T

b

T

l

T

b

T

l

T

b

T

l

T

b

δ

f

δ

f

T

c

δ

f

i+4

Loading...

Loading...