Stack Alignment D

D-3

As an optimization, an alternate entry point can be created that can be

called when proper stack alignment is provided by the caller. Using call

graph profiling of the VTune analyzer, calls to the normal (unaligned)

entry point can be optimized into calls to the (alternate) aligned entry

point when the stack can be proven to be properly aligned. Furthermore,

a function alignment requirement attribute can be modified throughout

the call graph so as to cause the least number of calls to unaligned entry

points. As an example of this, suppose function F has only a stack

alignment requirement of 4, but it calls function G at many call sites,

and in a loop. If G’s alignment requirement is 16, then by promoting F’s

alignment requirement to 16, and making all calls to G go to its aligned

entry point, the compiler can minimize the number of times that control

passes through the unaligned entry points. Example D-1 and

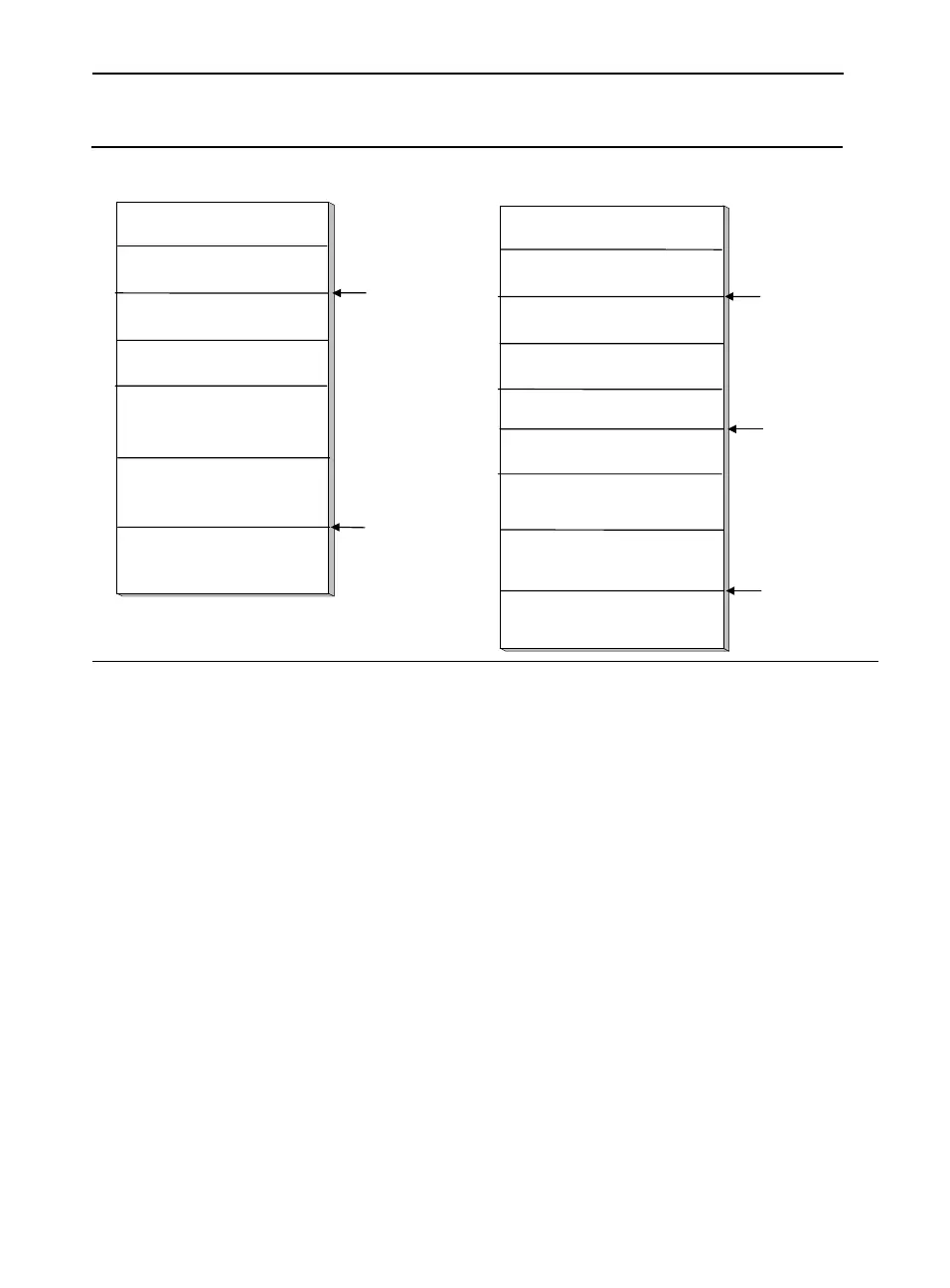

Figure D-1 Stack Frames Based on Alignment Type

Parameter

Pointer

EBP

ESP

EBP-based Aligned Frame

Parameters

Return Address

Padding

Previous EBP

Local Variables and

Spill Slots

Parameter Passing

Space

EBP-frame Saved

Register Area

Return Address 1

SEH/CEH Record

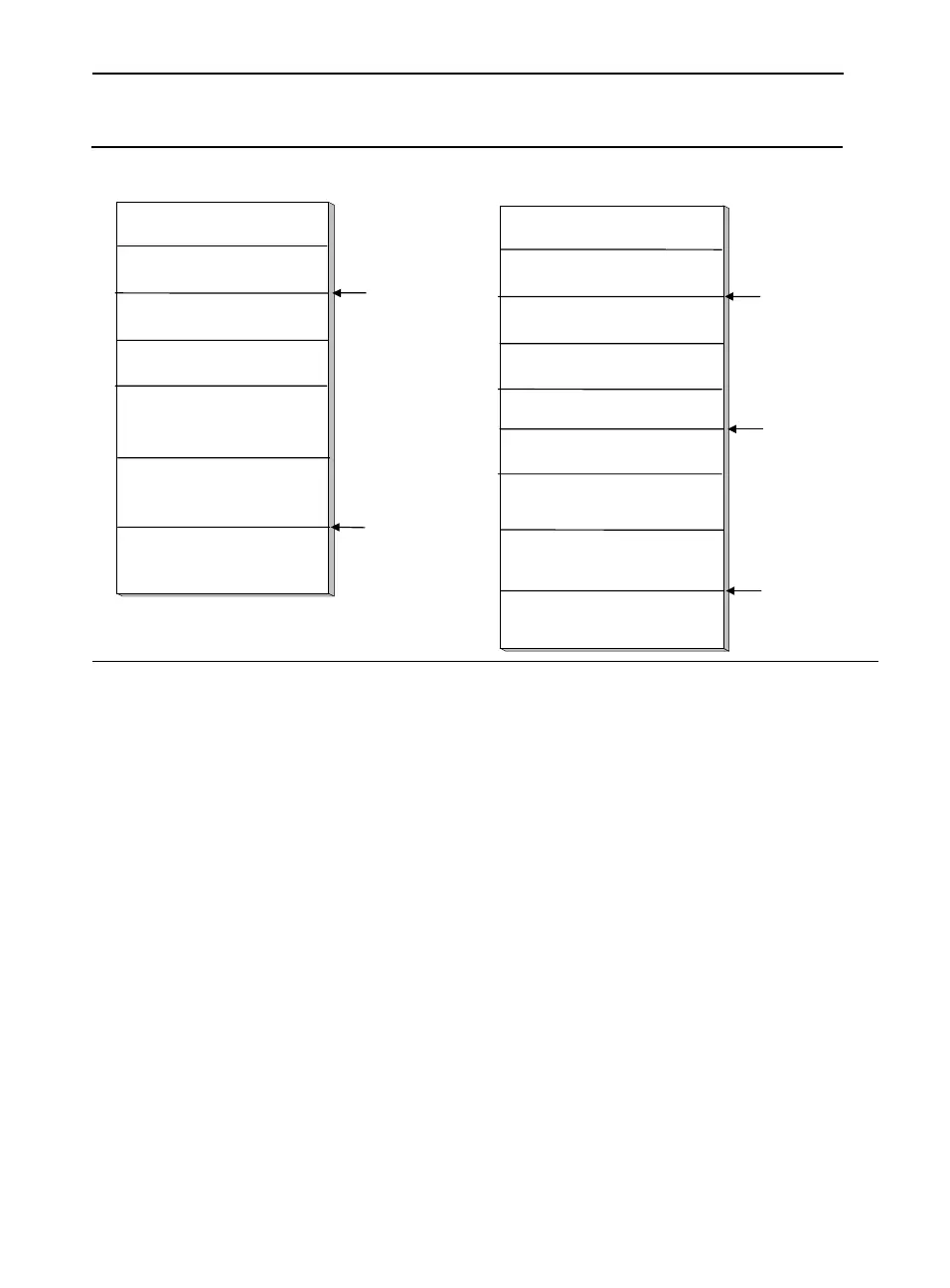

Parameter

Pointer

ESP

ESP-based Aligned Frame

Parameters

Return Address

Padding

Register Save Area

Local Variables and

Spill Slots

__cdecl Parameter

Passing Space

__stdcall Parameter

Passing Space

Loading...

Loading...