IA-32 Intel® Architecture Optimization

A-10

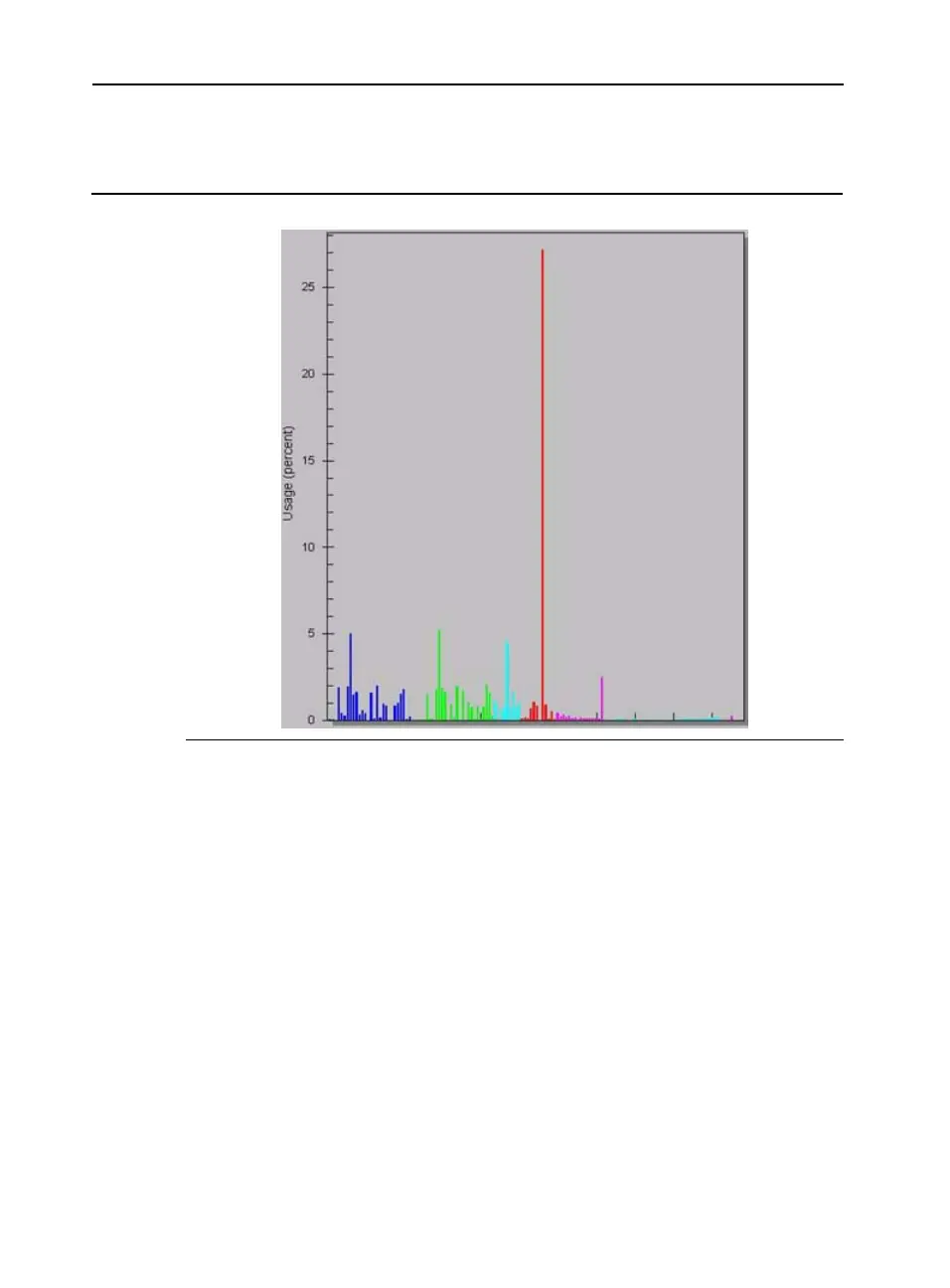

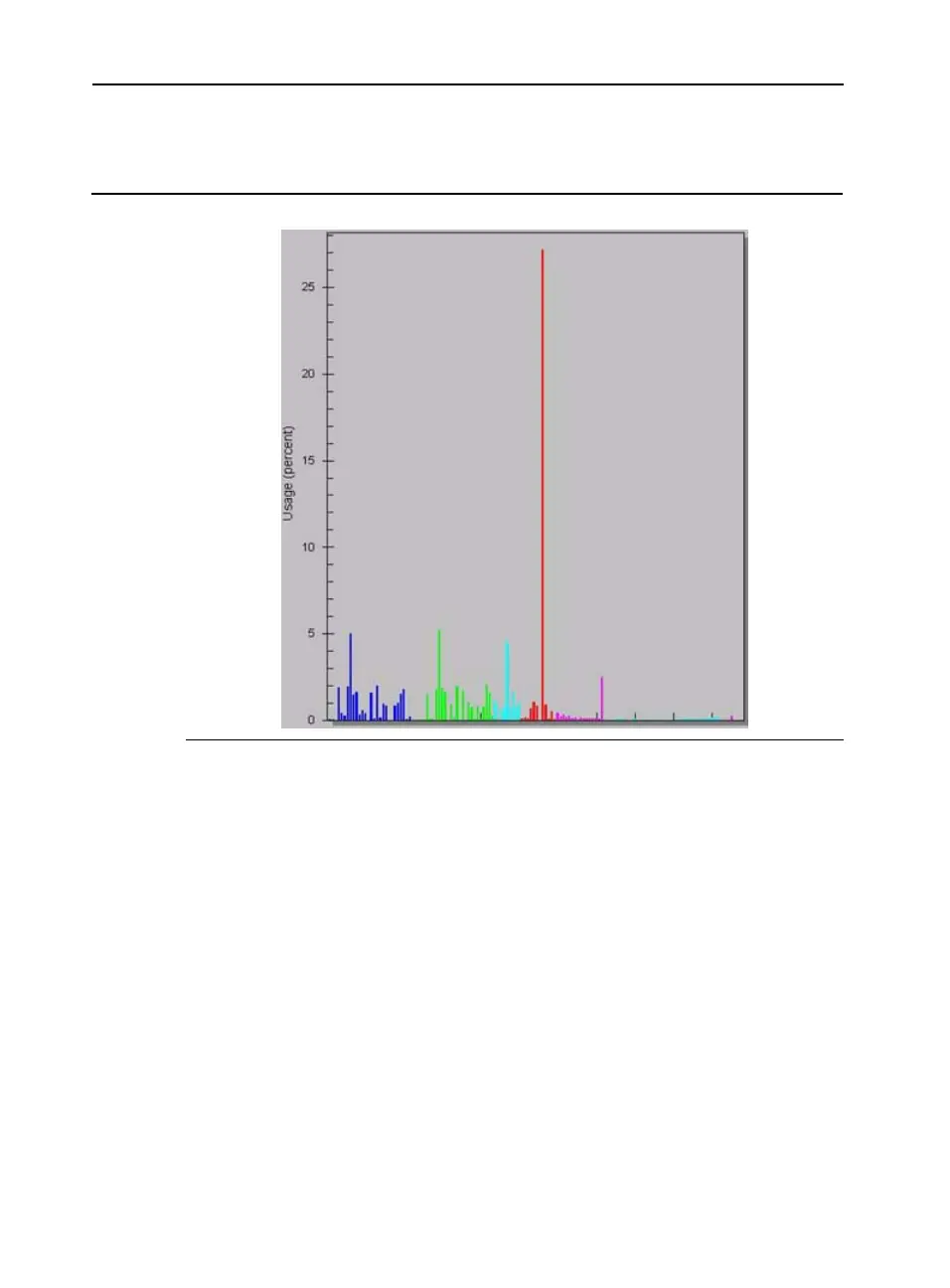

Figure A-1 provides an example of a hotspots report by location.

Event-based Sampling

Event-based sampling (EBS) can be used to provide detailed

information on the behavior of the microprocessor as it executes

software. Some of the events that can be used to trigger sampling

include clockticks, cache misses, and branch mispredictions. The

VTune analyzer indicates where micro architectural events, specific to

the Pentium 4, Pentium M and Intel Xeon processors, occur the most

often. On Pentium M processors, the VTune analyzer can collect two

Figure A-1 Sampling Analysis of Hotspots by Location

Loading...

Loading...