IA-32 Intel® Architecture Optimization

4-14

Insert Word

The pinsrw instruction loads a word from the lower half of a 32-bit

integer register or from memory and inserts it in the MMX technology

destination register at a position defined by the two least significant bits

of the immediate constant. Insertion is done in such a way that the three

other words from the destination register are left untouched, see

Figure 4-6 and Example 4-8.

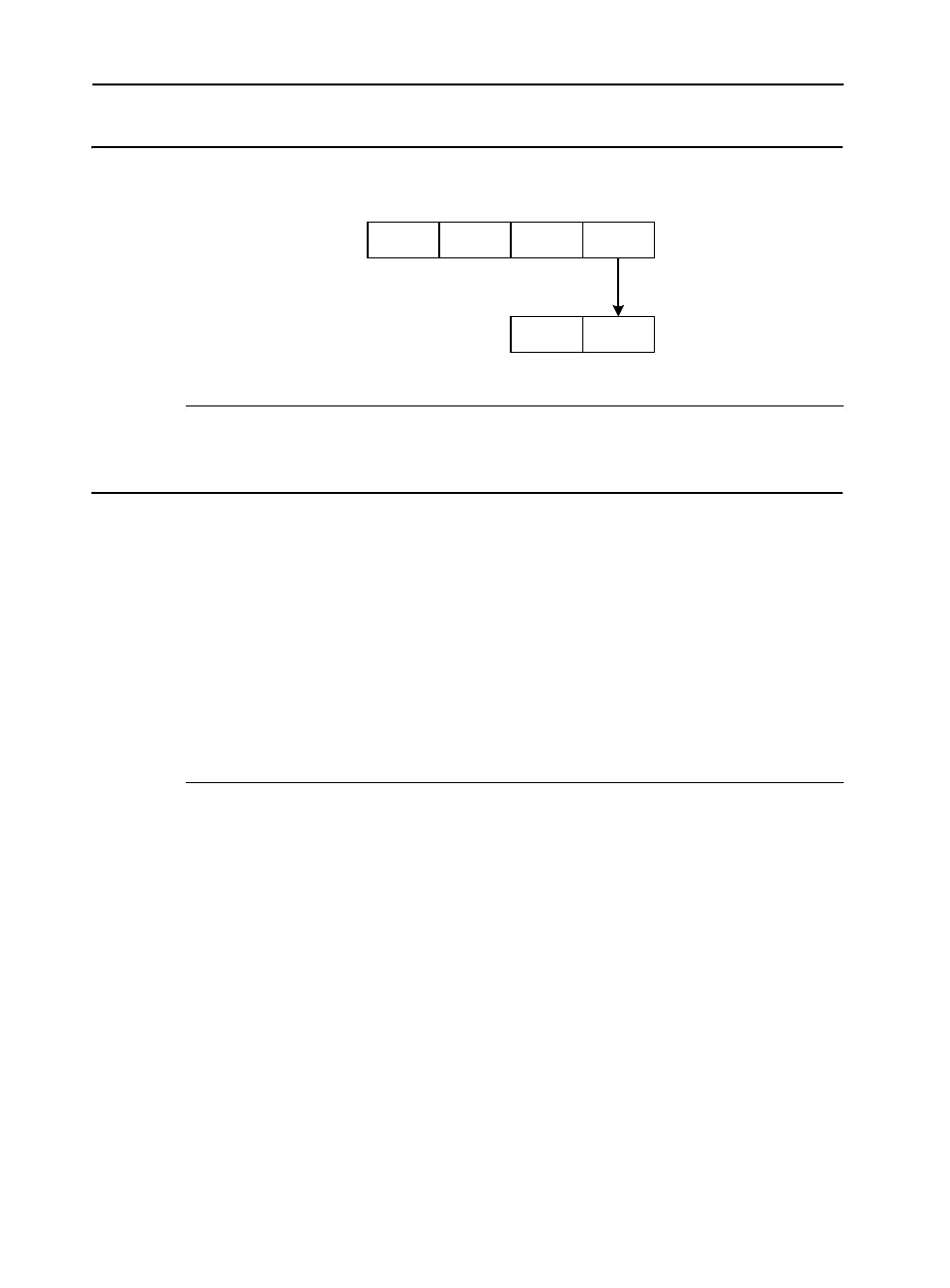

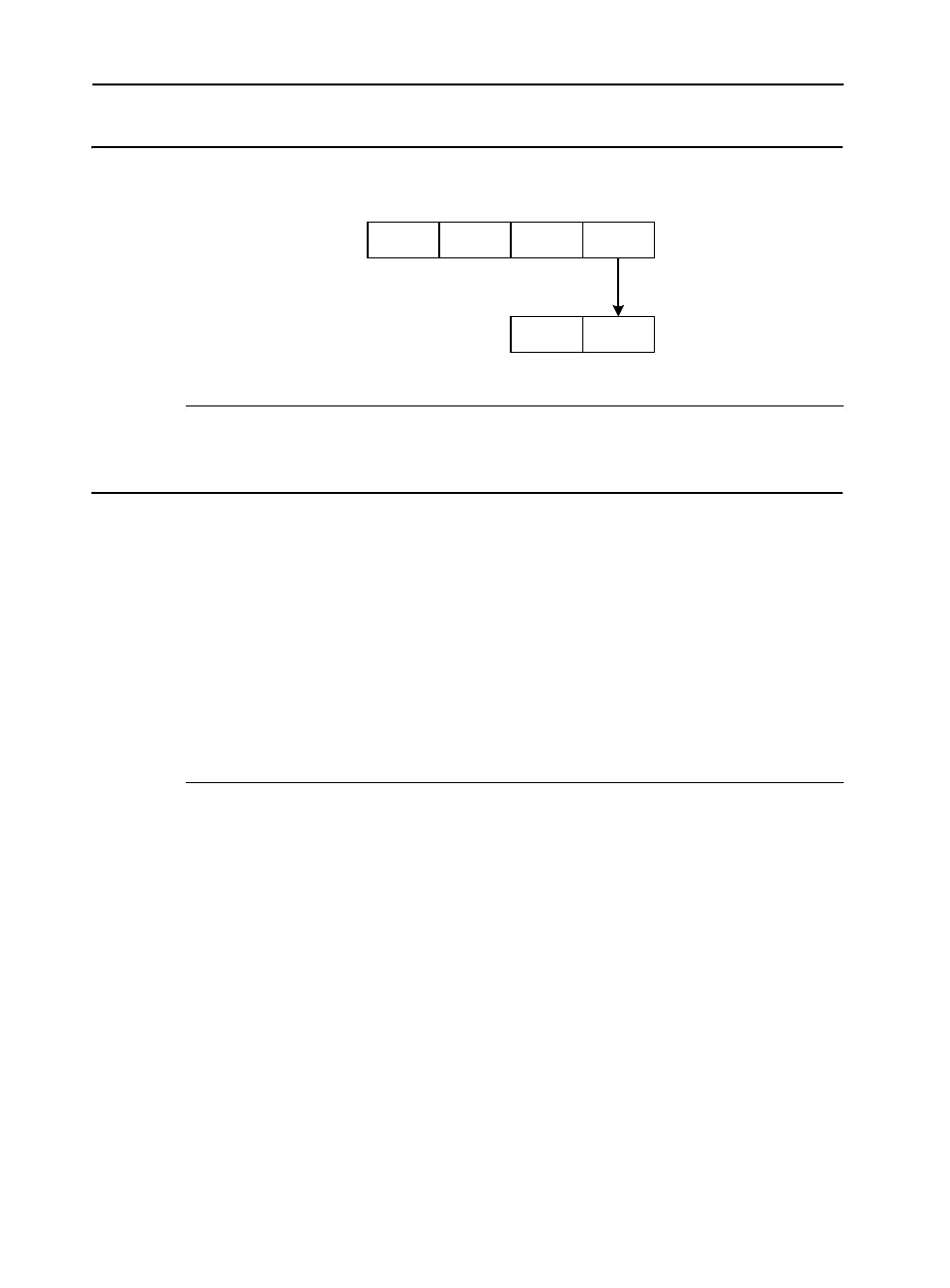

Figure 4-5 pextrw Instruction

Example 4-7 pextrw Instruction Code

; Input:

; eax source value

; immediate value:“0”

; Output:

; edx 32-bit integer register containing the

; extracted word in the low-order bits &

; the high-order bits zero-extended

movq mm0, [eax]

pextrw edx, mm0, 0

OM15163

0 ..0 X1

MM

R32

31 0

31 063

X4 X3 X2 X1

Loading...

Loading...