IA-32 Intel® Architecture Optimization

7-12

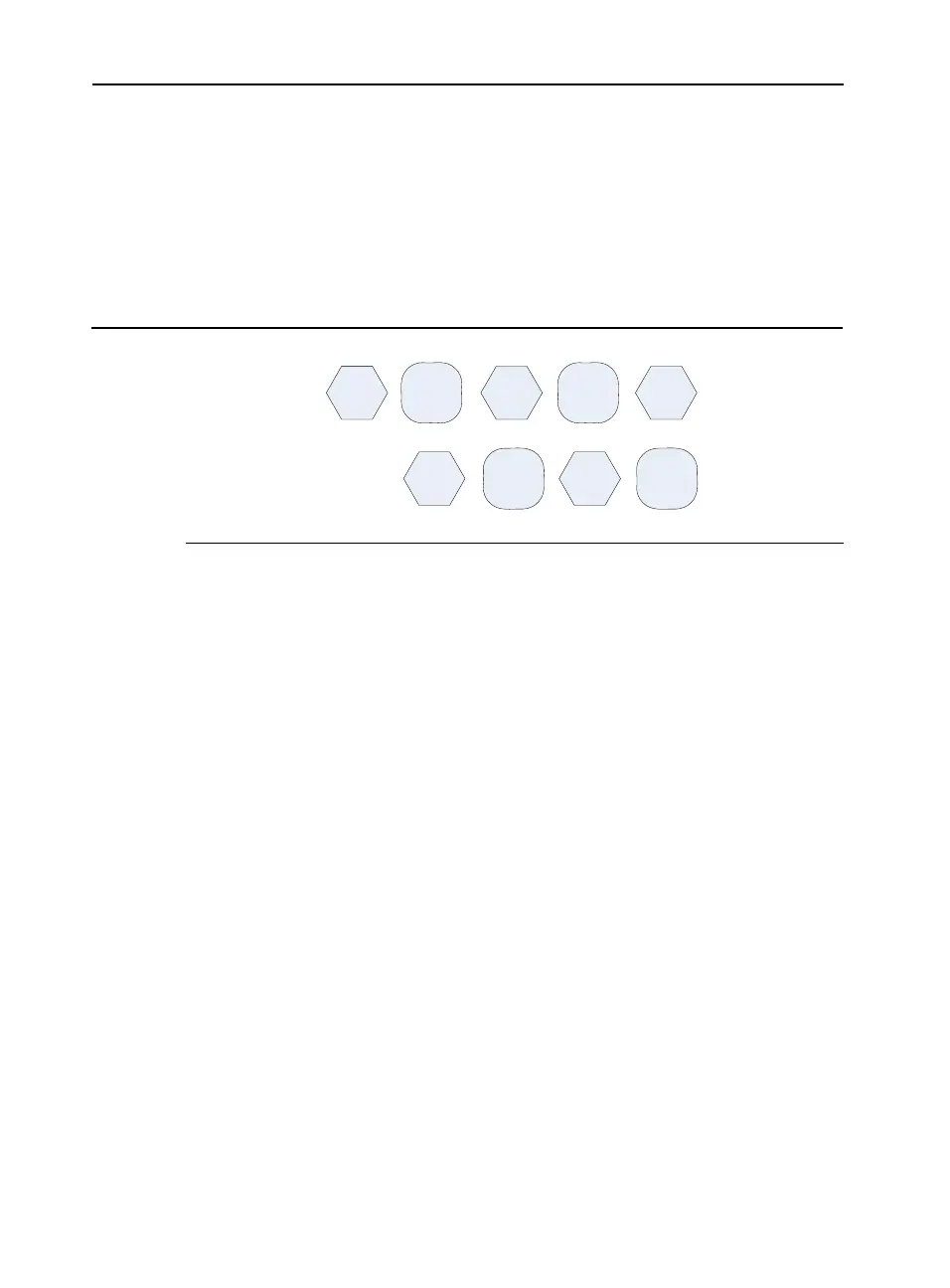

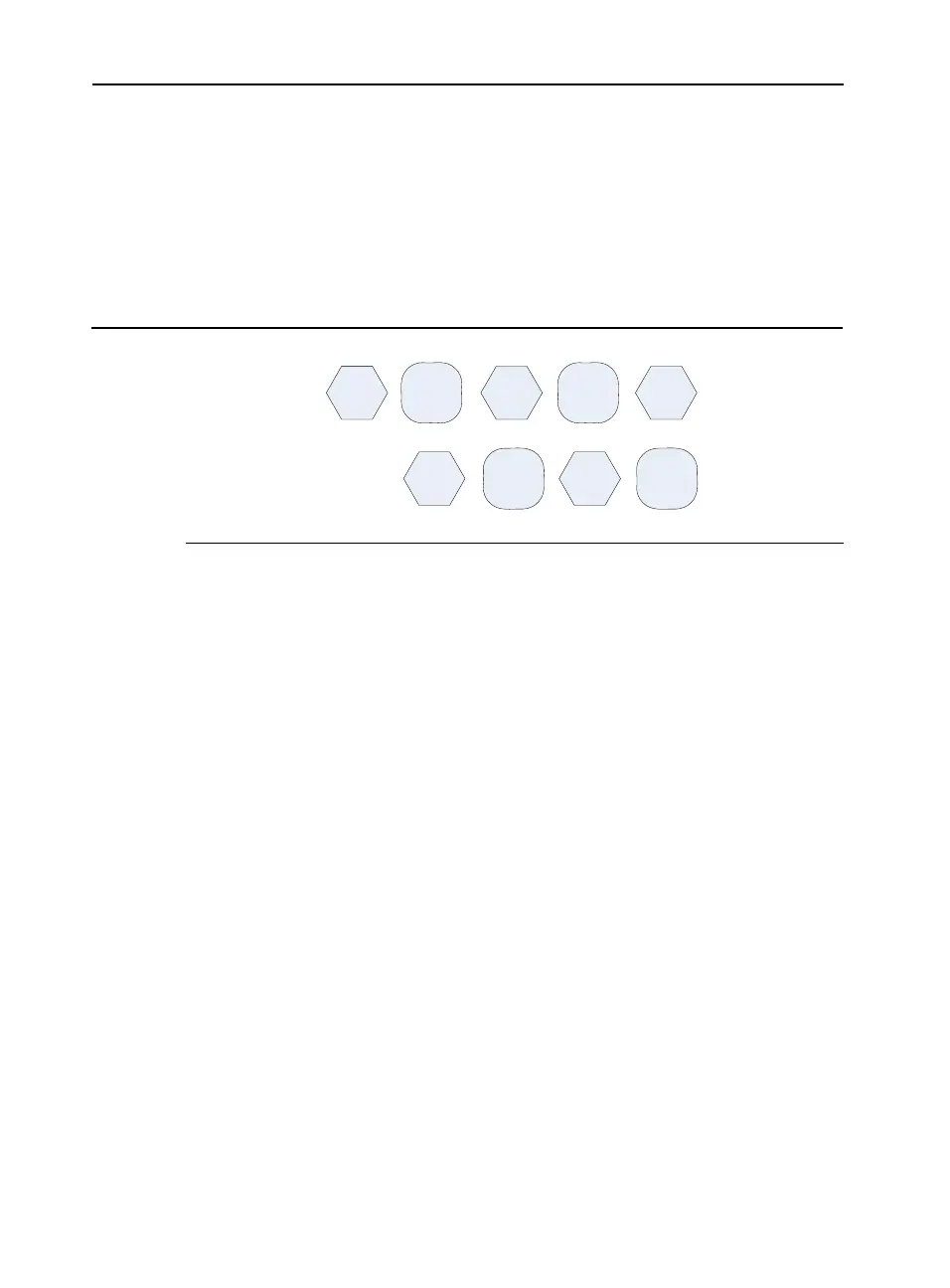

corresponding task to use its designated buffer. Thus, the producer and

consumer tasks execute in parallel in two threads. As long as the data

generated by the producer reside in either the first or second level cache

of the same core, the consumer can access them without incurring bus

traffic. The scheduling of the interlaced producer-consumer model is

shown in Figure 7-4.

Example 7-3 shows the basic structure of a thread function that can be

used in this interlaced producer-consumer model.

Figure 7-4 Interlaced Variation of the Producer Consumer Model

P(2)

P(1)

P(2)

P(1) C(1)

C(2)

C(1)

C(2)

P(1)

Thread 0

Thread 1

Loading...

Loading...