IA-32 Intel® Architecture Optimization

9-12

Using Enhanced Intel SpeedStep

®

Technology

Use Enhanced Intel SpeedStep Technology to adjust the processor to

operate at a lower frequency and save energy. The basic idea is to divide

computations into smaller pieces and use OS power management policy

to effect a transition to higher P-states.

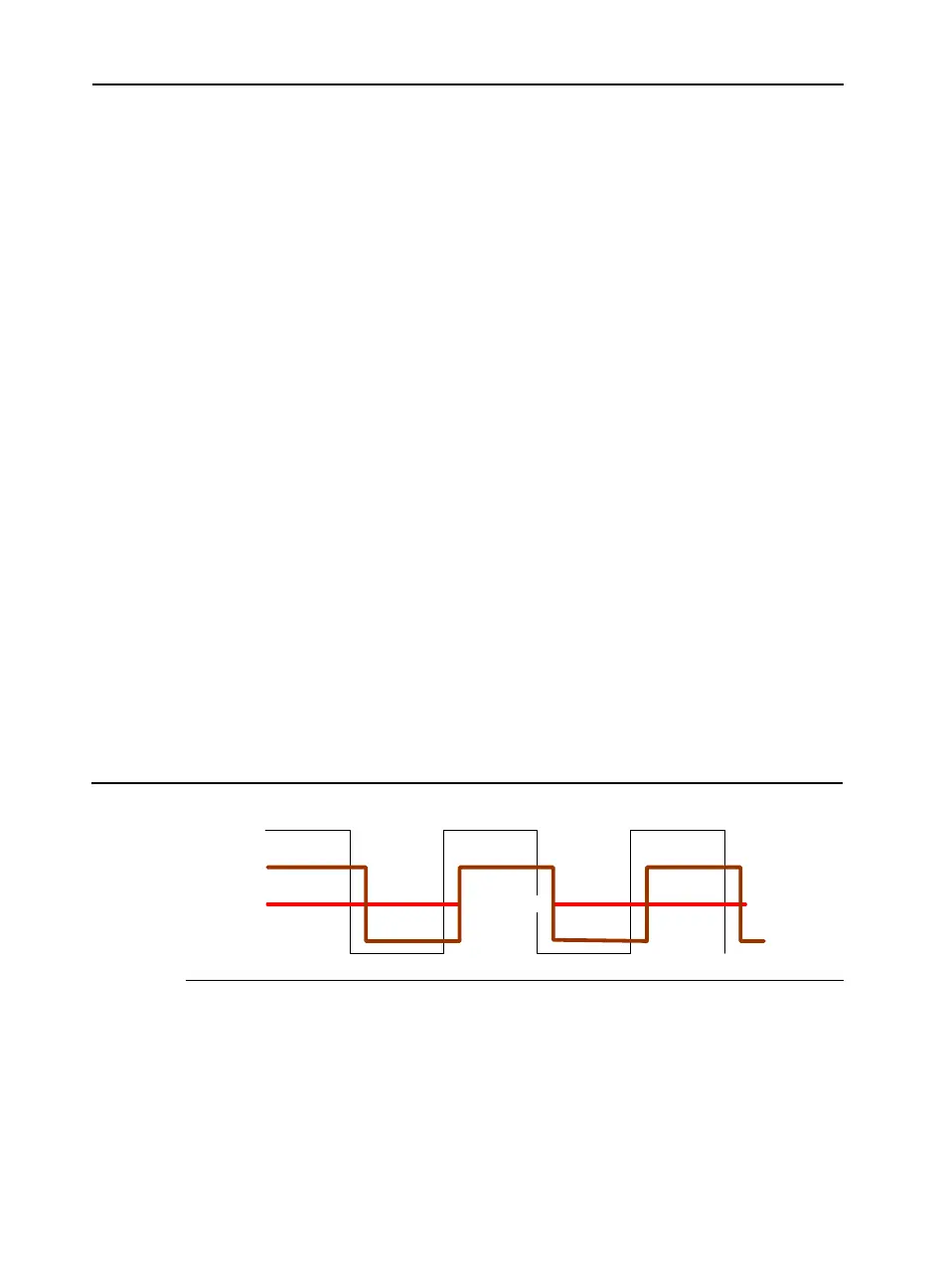

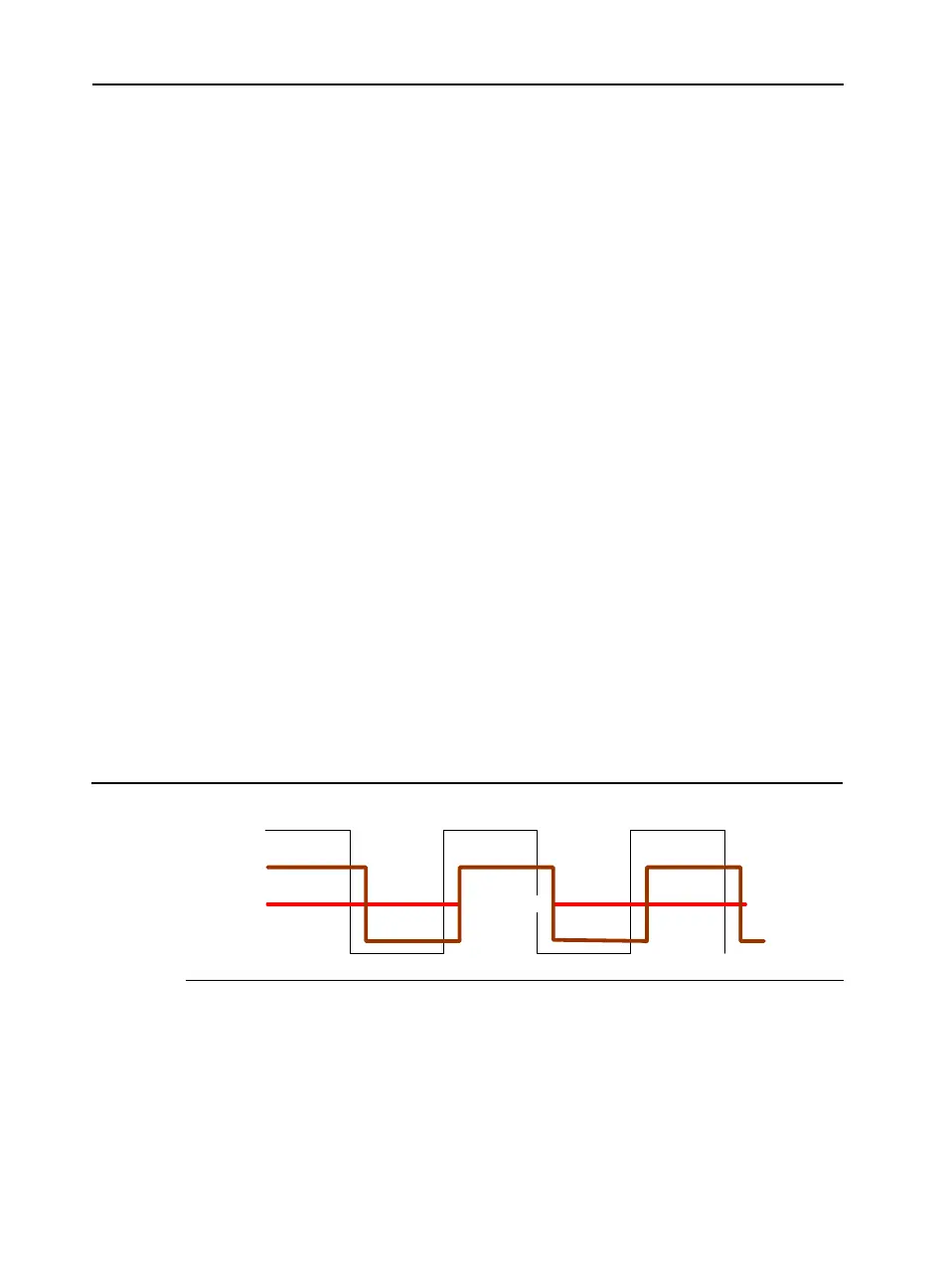

Typically, OSs use a time constant on the order of 10s to 100s of

milliseconds

6

to detect demand on processor workload. For example,

consider an application that requires only 50% of processor resources to

reach a required quality of service (QOS). The scheduling of tasks

occurs in such a way that the processor needs to stay in P0 state (highest

frequency to deliver highest performance) for 0.5 seconds and may then

goes to sleep for 0.5 seconds. The demand pattern then alternates.

Thus the processor demand switches between 0 and 100% every 0.5

seconds, resulting in an average of 50% of processor resources. As a

result, the frequency switches accordingly between the highest and

lowest frequency. The power consumption also switches in the same

manner, resulting in an average power usage represented by the

equation Paverage = (Pmax+Pmin)/2.

Figure 9-4 illustrates the chronological profiles of coarse-grain (> 300

ms) task scheduling and its effect on operating frequency and power

consumption.

6. The actual number may vary by OS and by OS release.

Figure 9-4 Profiles of Coarse Task Scheduling and Power Consumption

CPU demand

Average power

Frequency

& Power

Loading...

Loading...