IA-32 Intel® Architecture Optimization

A-20

Intel

®

Software College

The Intel

®

Software College is a valuable resource for classes on

Streaming SIMD Extensions 2 (SSE2), Threading and the IA-32 Intel

Architecture. For online training on how to use the SSE2 and

Hyper-Threading Technology, refer to the IA-32 Architecture Training -

Online Training at

http://developer.intel.com/software/college/CourseCatalog.asp?CatID=

web-based. For key algorithms and their optimization examples for the

Pentium 4 processor, refer to the application notes. You can find

additional information on classroom training from the Intel Software

College Web site at http://developer.intel.com/software/college

, and

general information for developers from Intel Developer Services at

http://www.intel.com/ids

.

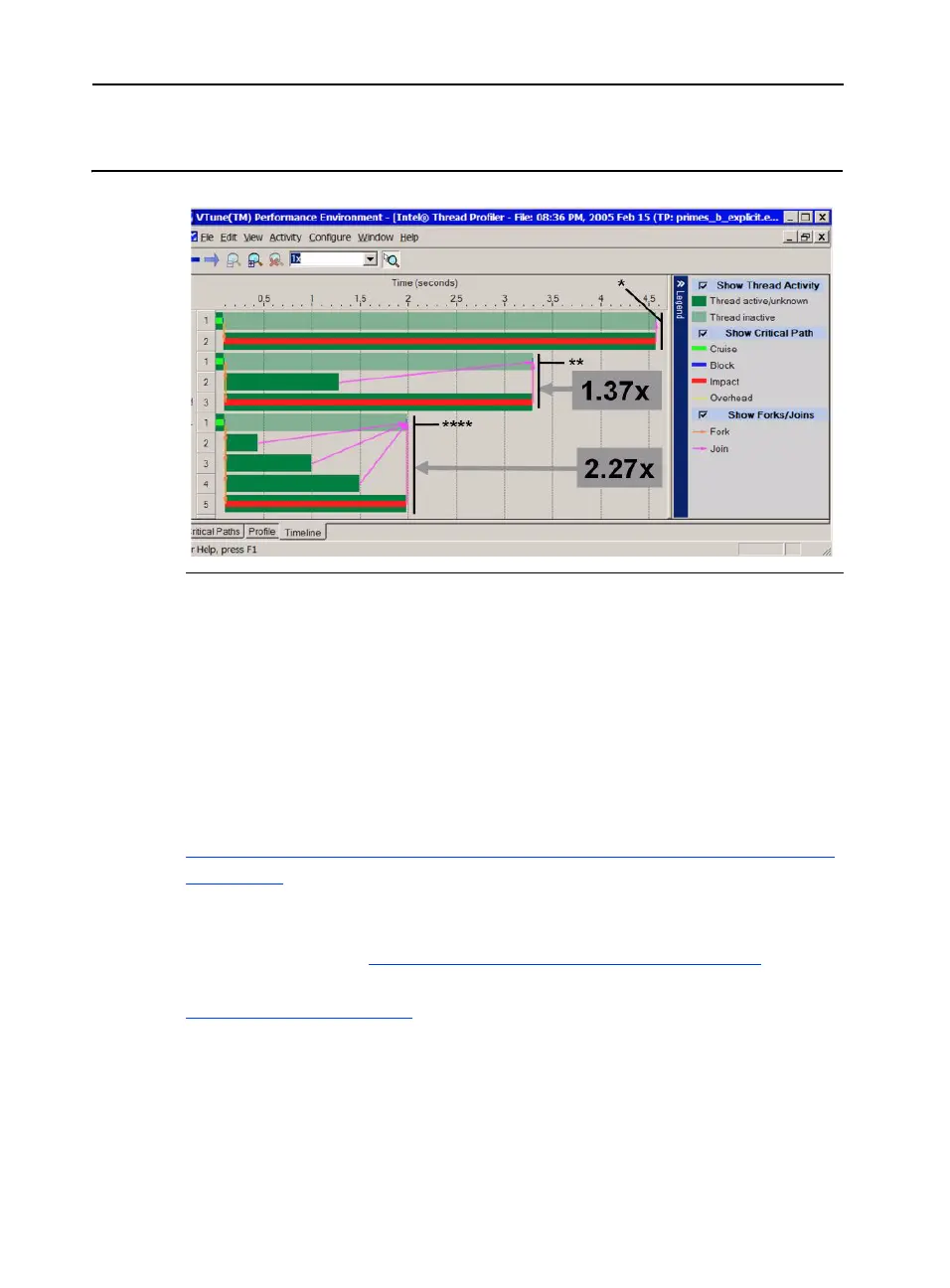

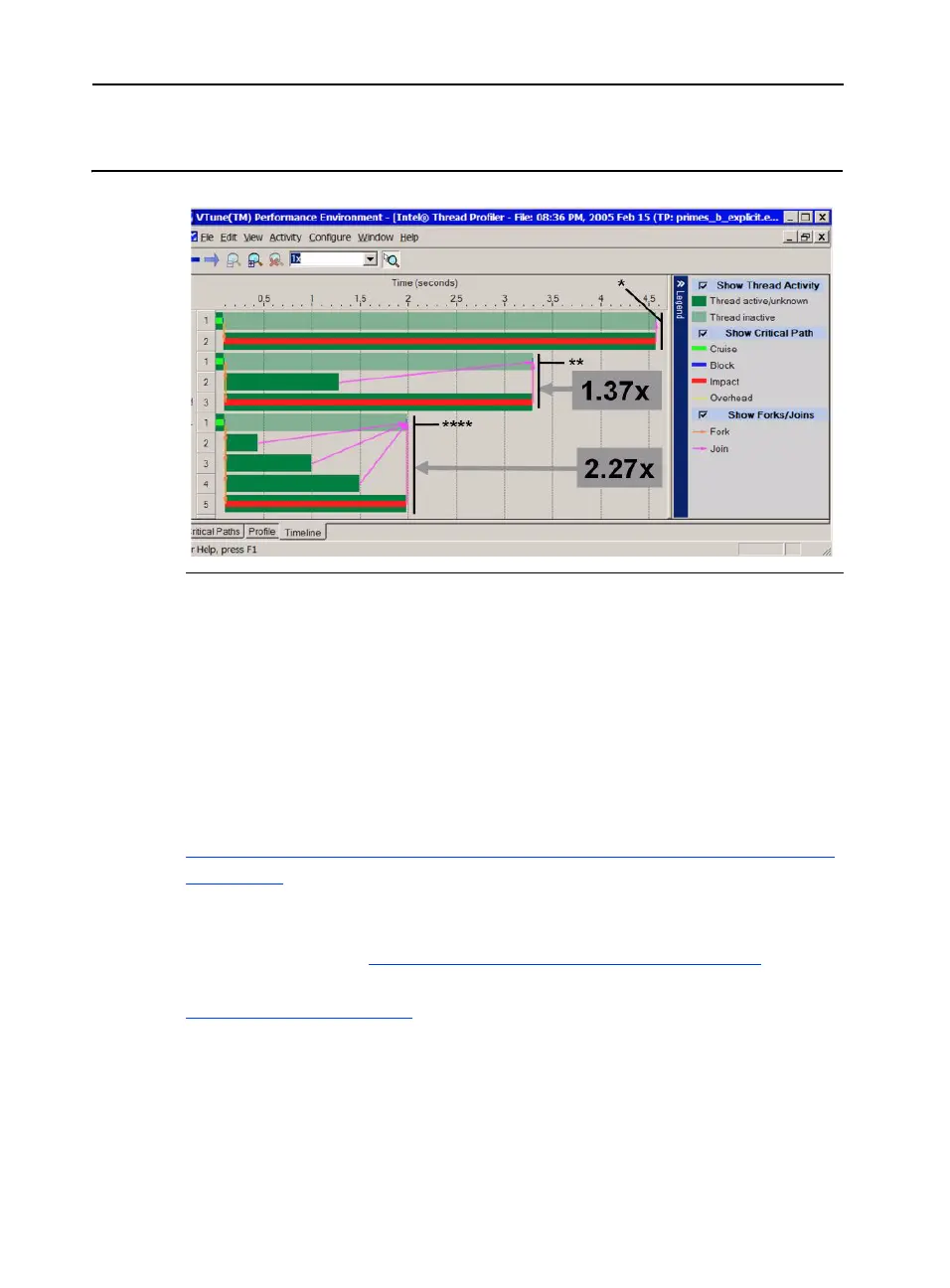

Figure A-3 Intel Thread Profiler Can Show Critical Paths of Threaded Execution

Timelines

Loading...

Loading...