Mathematics of Prefetch Scheduling Distance E

E-13

In reality, the front-side bus (FSB) pipelining depth is limited, that is,

only four transactions are allowed at a time in the Pentium III and

Pentium 4 processors. Hence a transaction bubble or gap, T

g

, (gap due

to idle bus of imperfect front side bus pipelining) will be observed on

FSB activities. This leads to consideration of the transaction gap in

computing the prefetch scheduling distance. The transaction gap, T

g

,

must be factored into the burst cycles, T

b

, for the calculation of prefetch

scheduling distance.

The following relationship shows computation of the transaction gap.

where T

l

is the memory leadoff latency, c is the number of chunks per

cache line and n is the FSB pipelining depth.

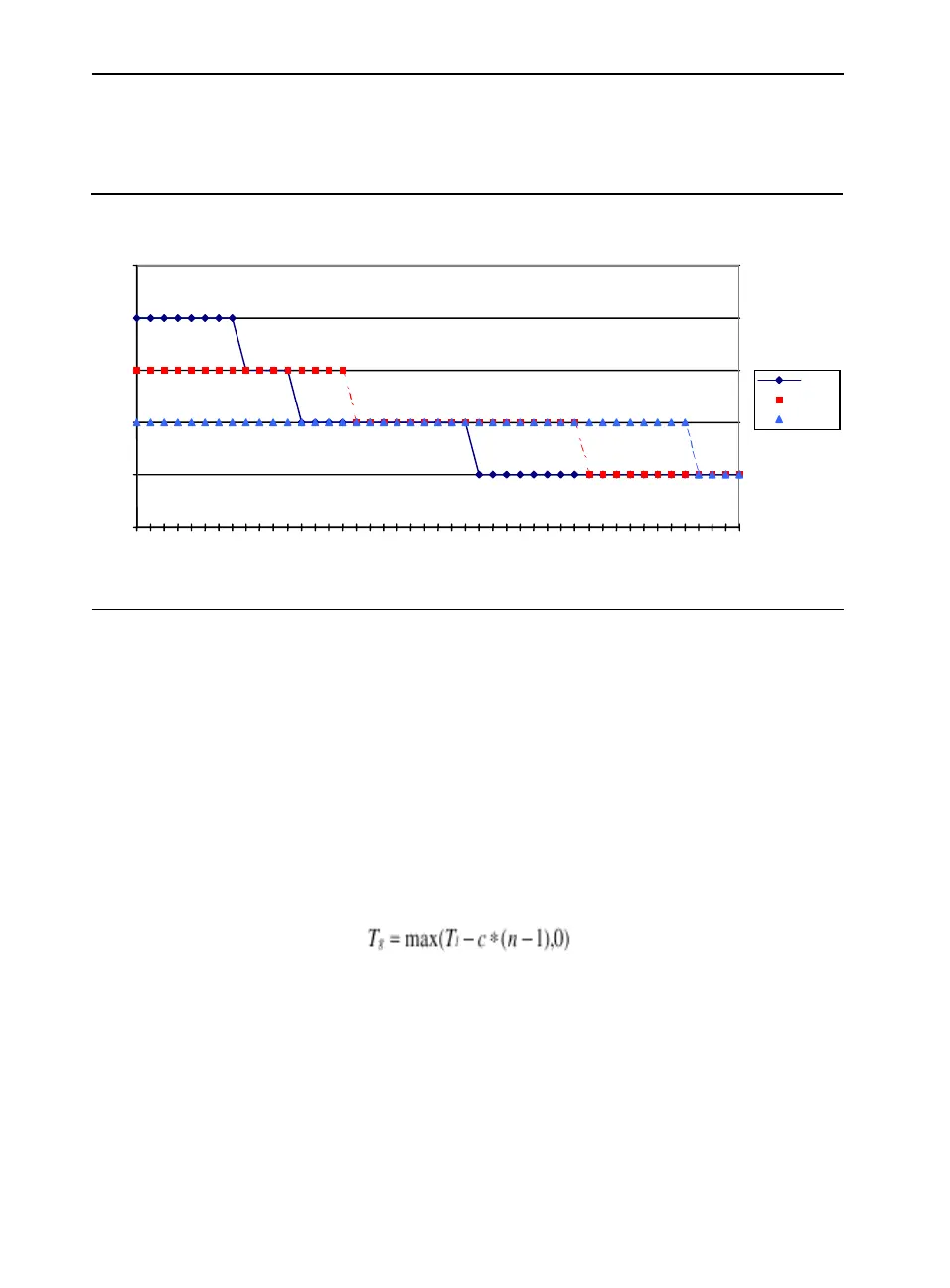

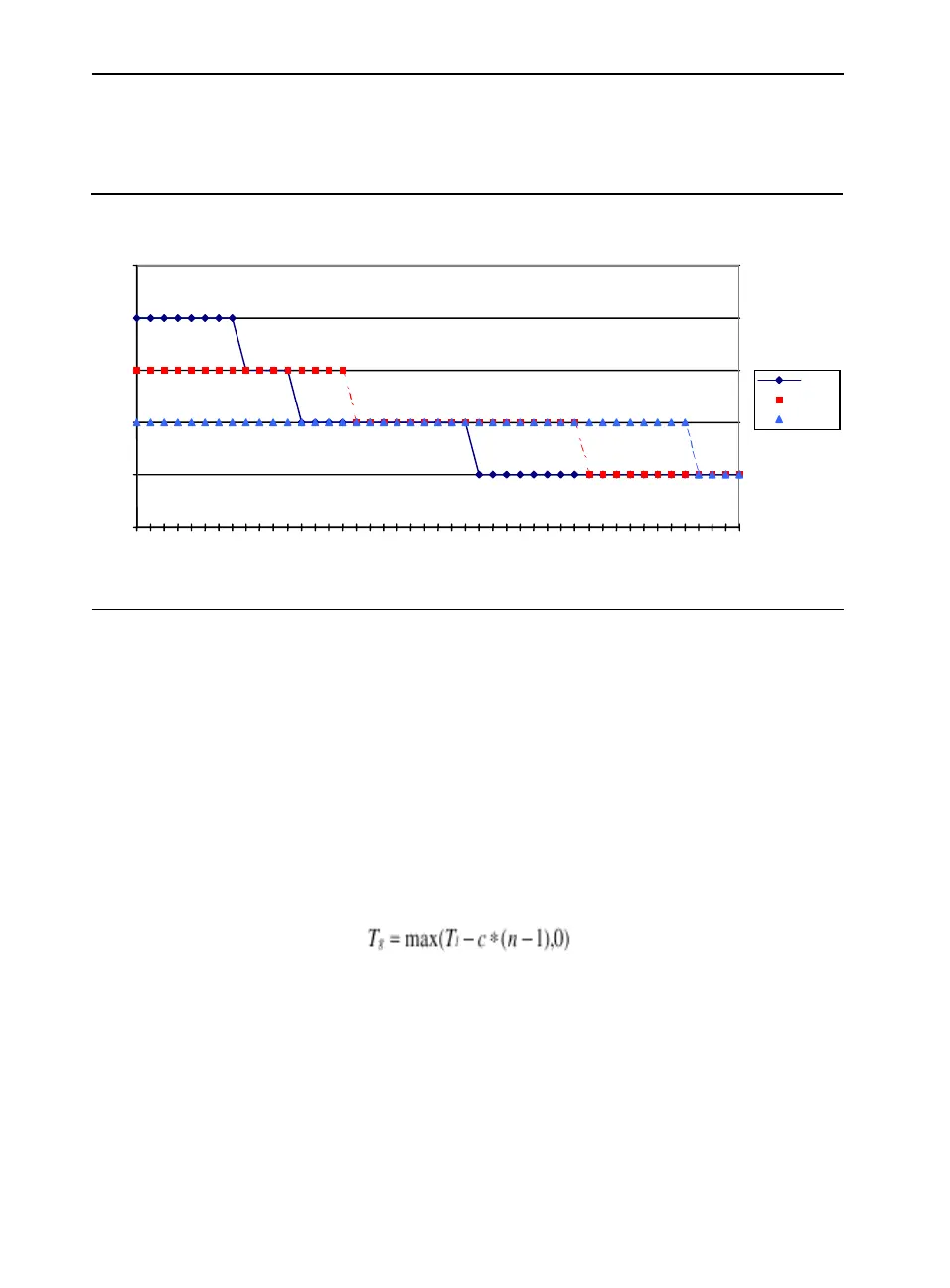

Figure E-7 Accesses per Iteration, Example 2

0

1

2

3

4

5

13579

11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45

Tc (in FSB clocks)

psd

2 lines

4 lines

6 lines

psd for different number of cache lines prefetched per iteration

Loading...

Loading...