IA-32 Intel® Architecture Optimization

9-6

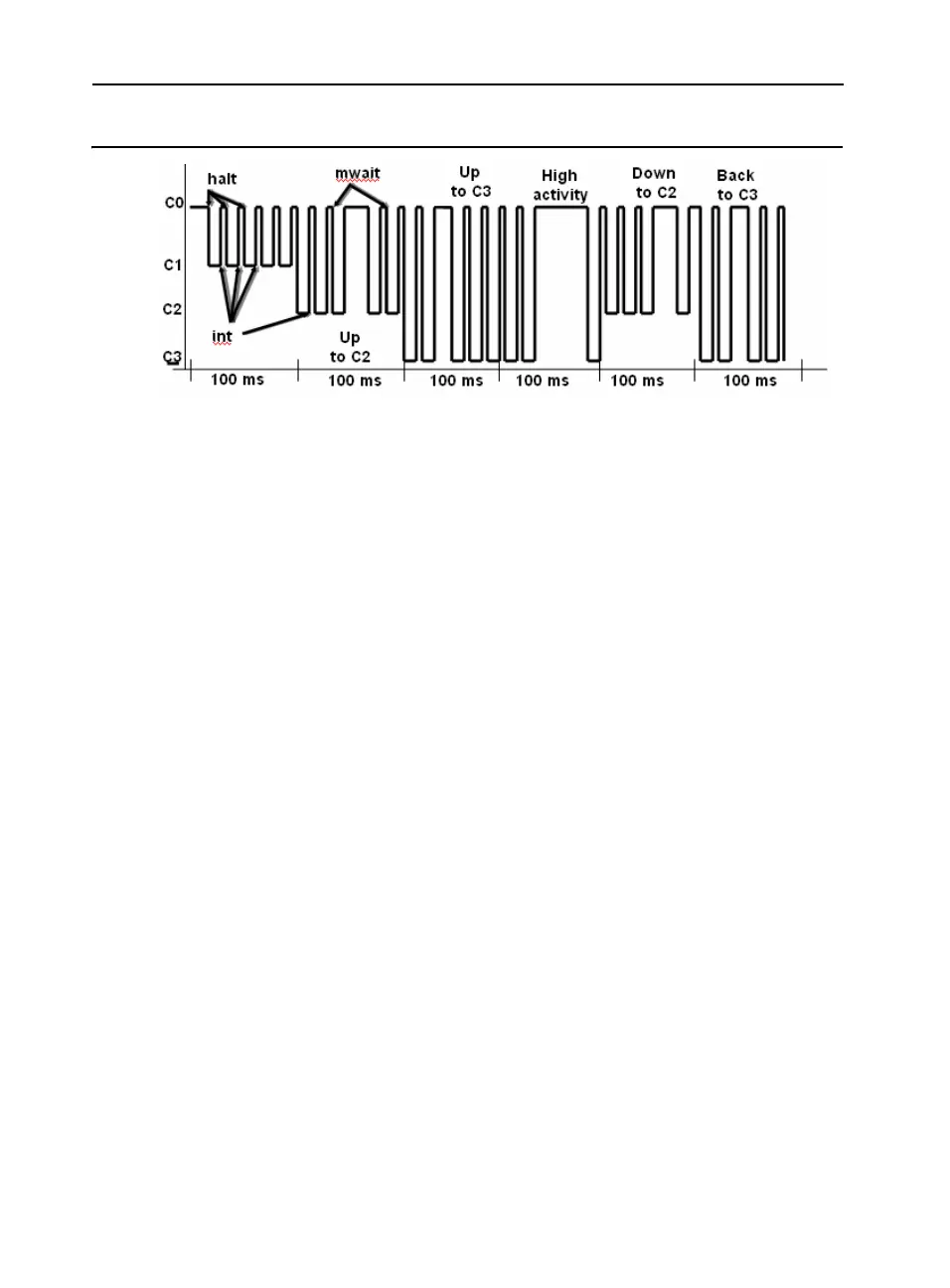

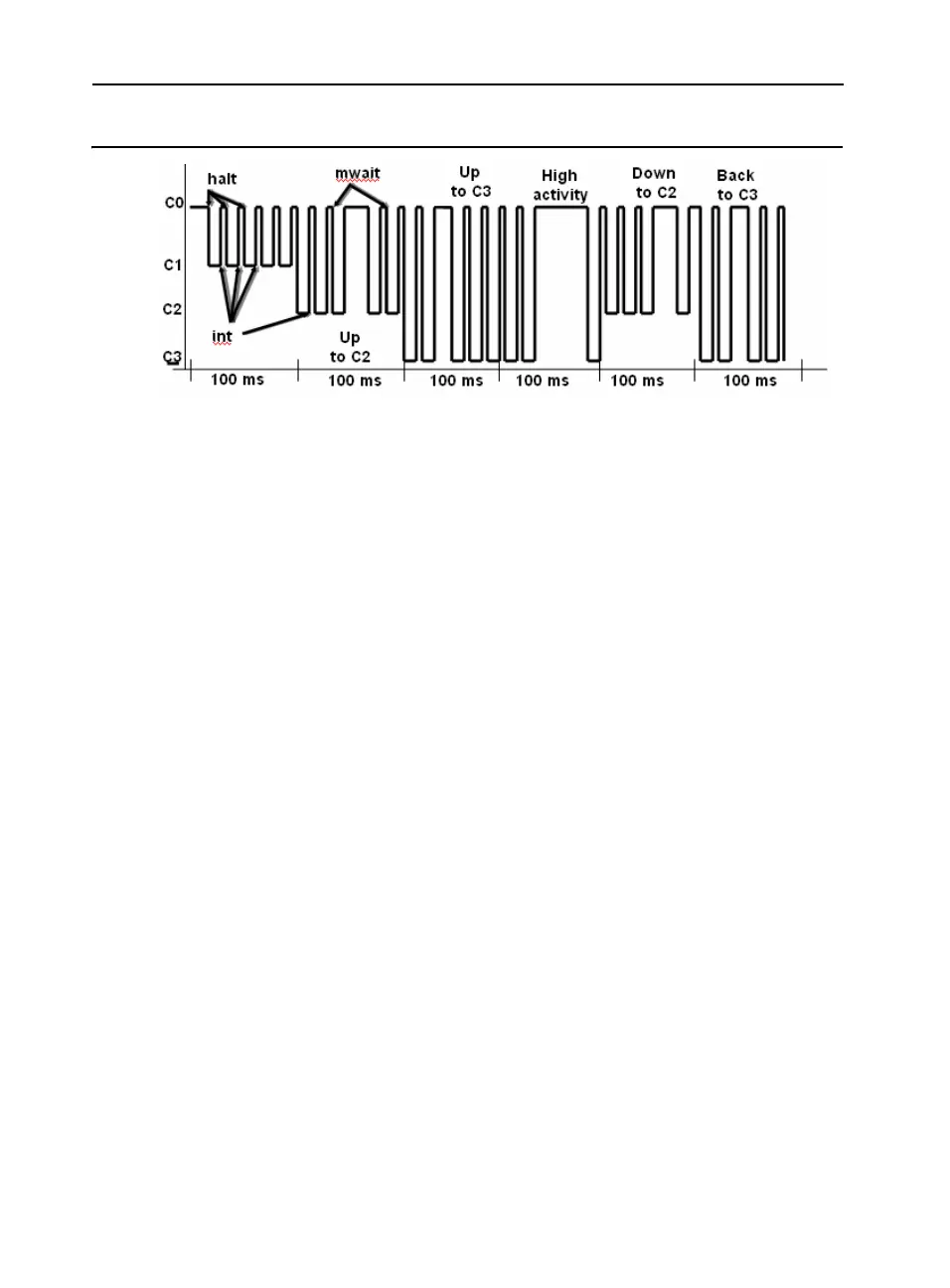

Figure 9-3 Application of C-states to Idle Time

Consider that a processor is in lowest frequency (LFM- low frequency

mode) and utilization is low. During the first time slice window (Figure

9-3 shows an example that uses 100 ms time slice for C-state decisions),

processor utilization is low and the OS decides to go to C2 for the next

time slice. After the second time slice, processor utilization is still low

and the OS decides to go into C3.

Processor-Specific C4 and Deep C4 States

The Pentium M, Intel Core Solo and Intel Core Duo processors

4

provide

additional processor-specific C-states (and associated sub C-states) that

can be mapped to ACPI C3 state type. The processor-specific C states

and sub C-states are accessible using MWAIT extensions (See CPUID

in IA-32 Intel® Architecture Software Developer’s Manual, Volume 2A).

One of the processor-specific state to reduce static power consumption

is referred to as C4 state. C4 provides power savings in the following

manner:

• The voltage of the processor is reduced to the lowest possible level

that still allows the L2 cache to maintain its state.

4. Pentium M processor can be detected by CPUID signature with family 6, model 9 or 13,

Intel Core Solo and Intel Core Duo processor has CPUID signature with family 6, model 14.

Loading...

Loading...