Power Optimization for Mobile Usages 9

9-17

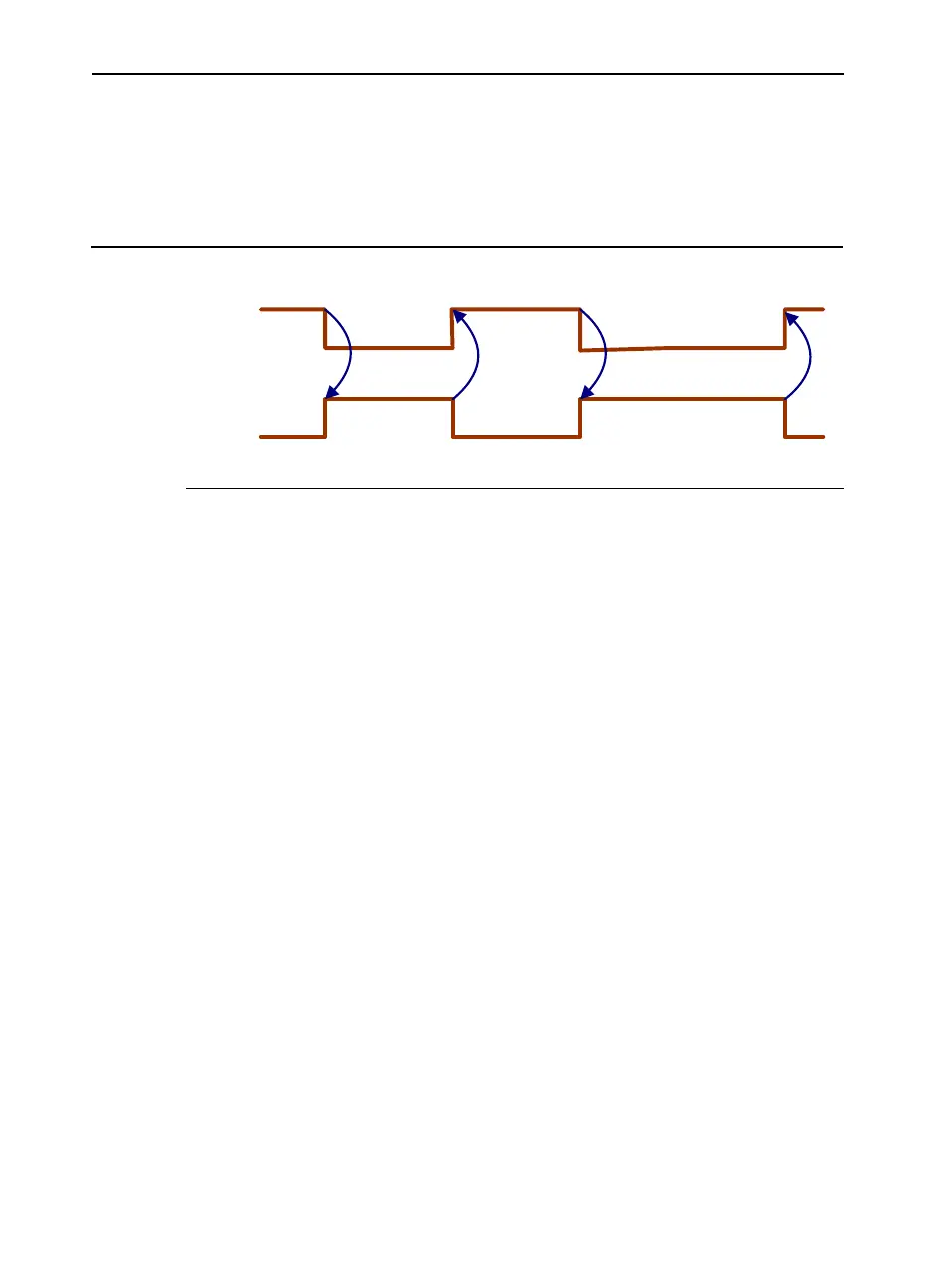

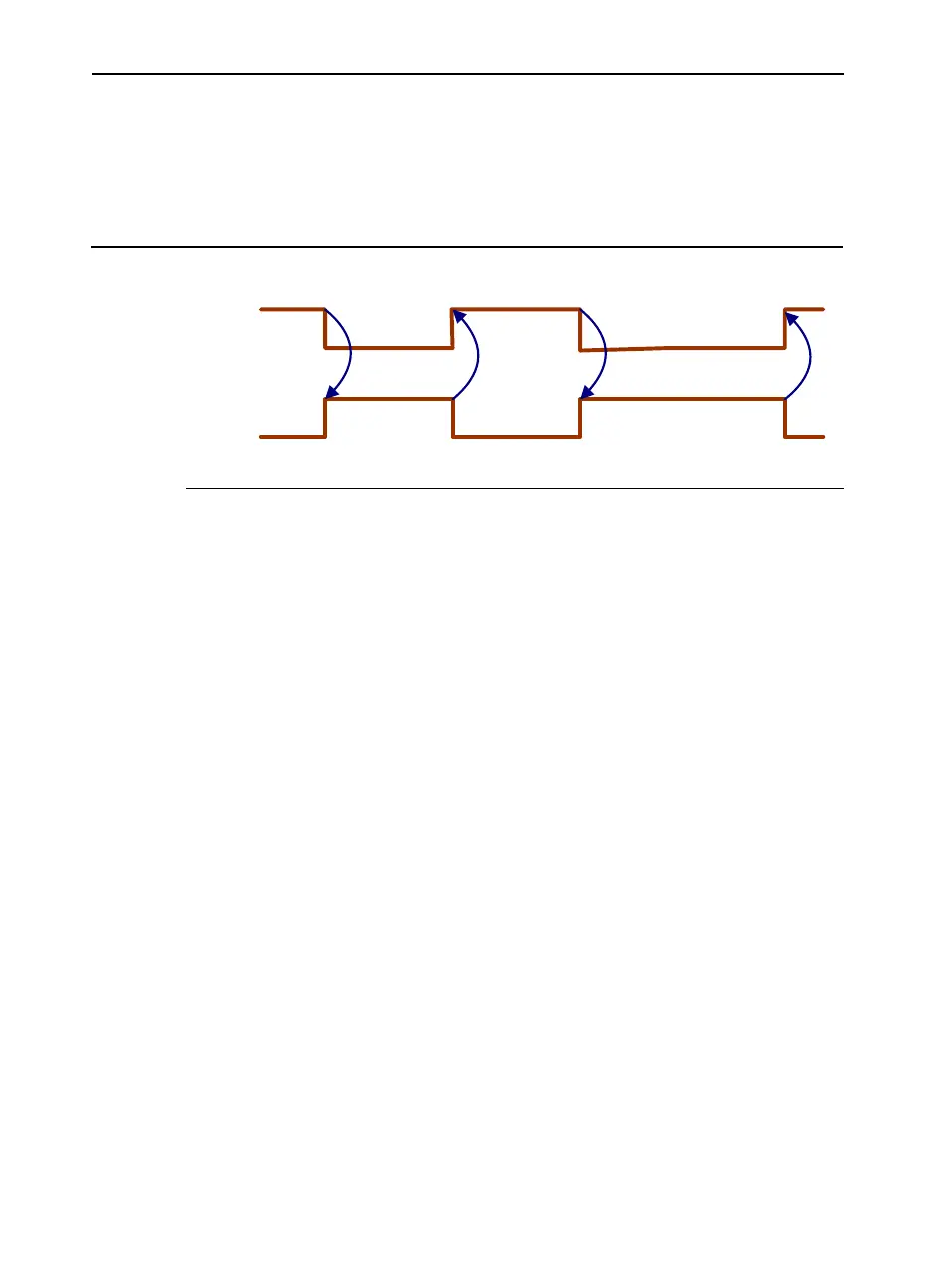

demands only 50% of processor resources (based on idle history). The

processor frequency may be reduced by such multi-core unaware P-state

coordination, resulting in a performance anomaly. See Figure 9-5:

Software applications have a couple of choices to prevent this from

happening:

• Thread affinity management: A multi-threaded application can

enumerate processor topology and assign processor affinity to

application threads to prevent thread migration. This can work

around the issue of OS lacking multi-core aware P-state

coordination policy.

• Upgrade to an OS with multi-core aware P-state coordination

policy: Some newer OS releases may include multi-core aware

P-state coordination policy. The reader should consult with specific

OS vendors.

Multi-core Considerations for C-States

There are two aspects that impact C-states on multi-core processors:

1. Multi-core-unaware C-state coordination may not fully realize

power savings.

When each core in a multi-core processor meets the

requirements necessary to enter a different C-state type,

multi-core-unaware hardware coordination causes the physical

Figure 9-5 Thread Migration in a Multi-Core Processor

Core 1

Core 2

active

Idle

active

Idle

Loading...

Loading...