Mathematics of Prefetch Scheduling Distance E

E-9

For this particular example the prefetch scheduling distance is greater

than 1. Data being prefetched for iteration i will be consumed in

iteration i+2.

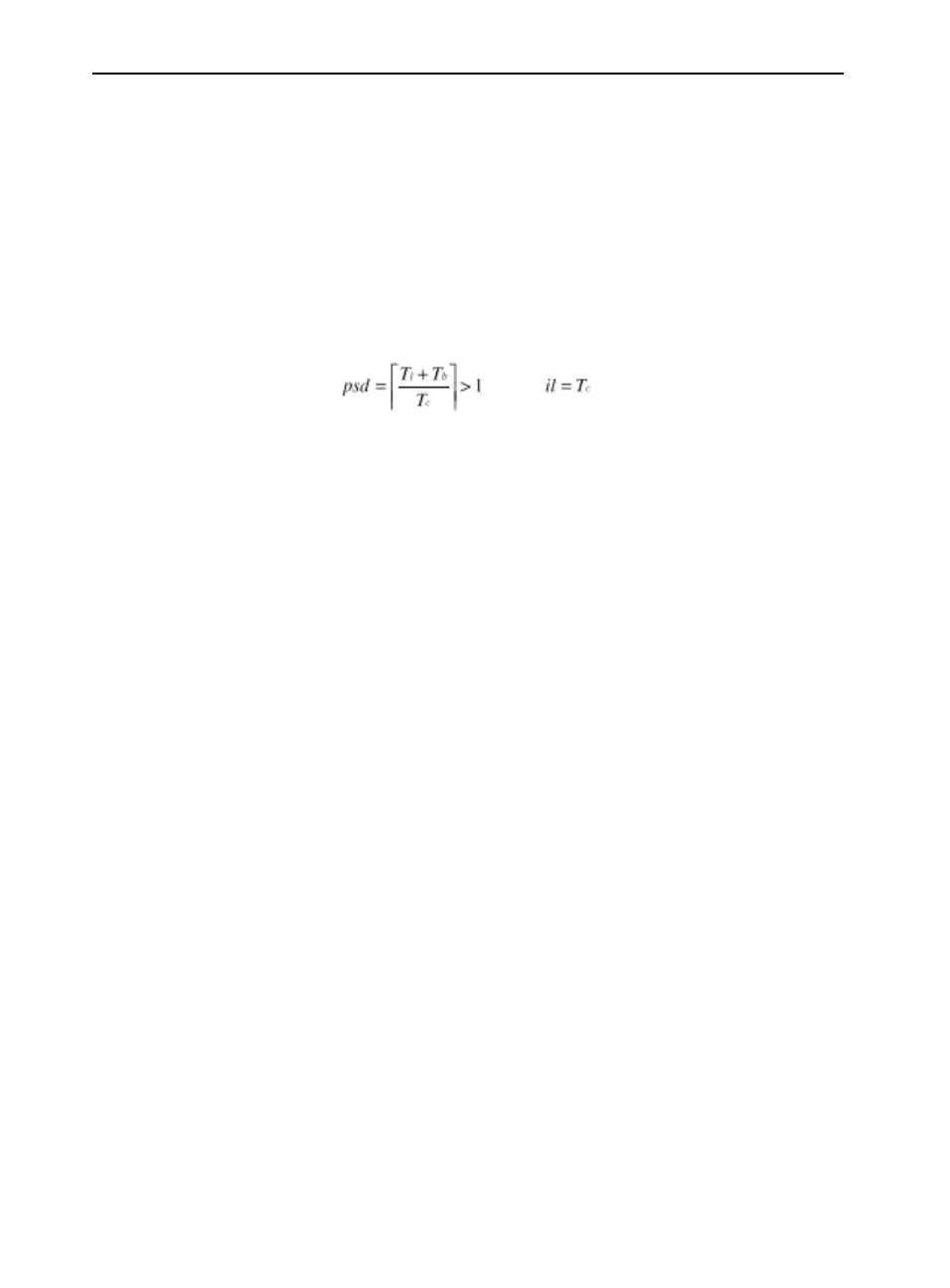

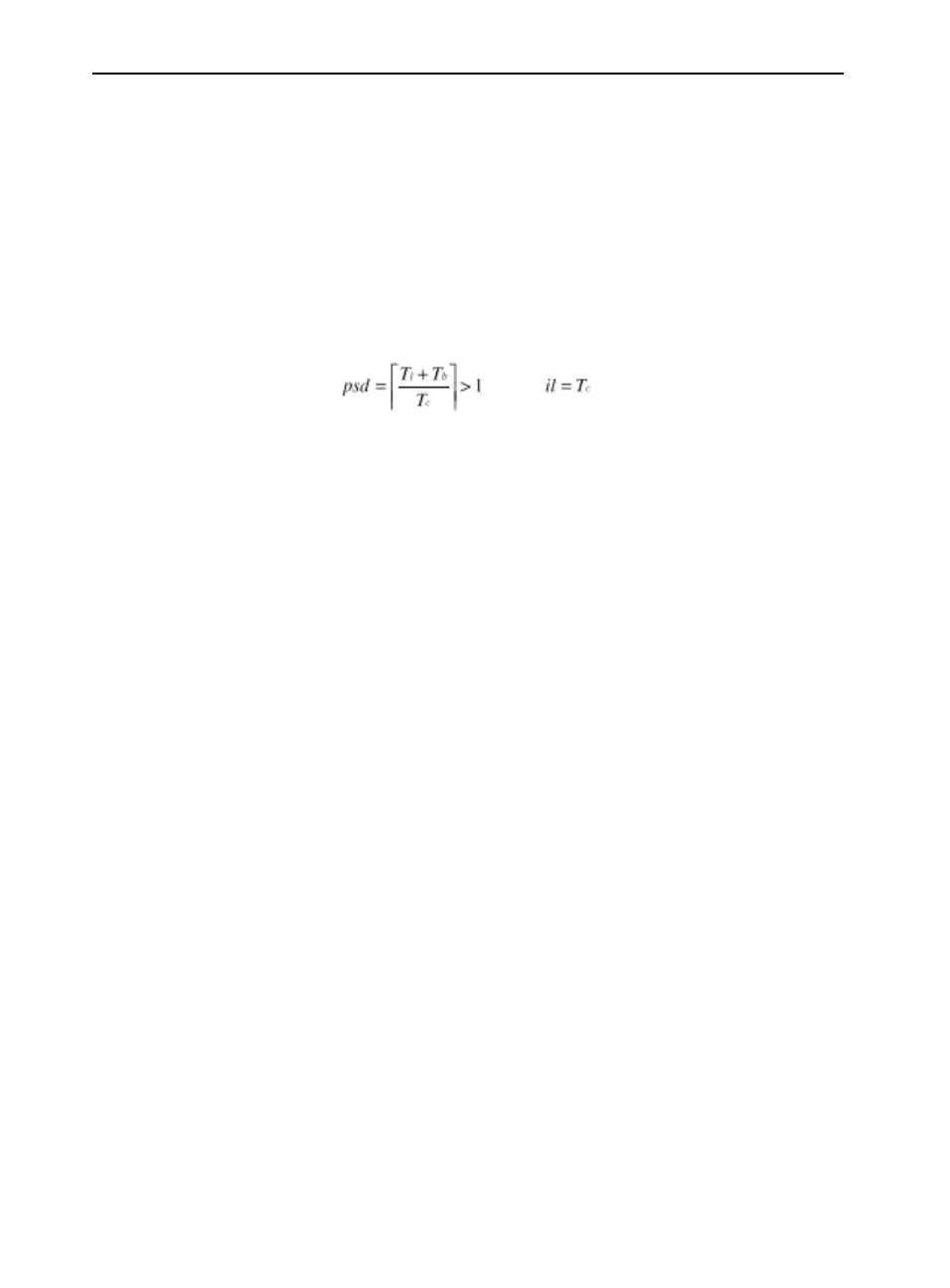

Figure E-4 represents the case when the leadoff latency plus data

transfer latency is greater than the compute latency, which is greater

than the data transfer latency. The following relationship can be used to

compute the prefetch scheduling distance.

In consequence, the iteration latency is also equal to the computation

latency, that is, compute bound program.

Loading...

Loading...