Ethernet (ETH): media access control (MAC) with DMA controller RM0090

1007/1422 Doc ID 018909 Rev 4

Ethernet DMA status register (ETH_DMASR)

Address offset: 0x1014

Reset value: 0x0000 0000

The Status register contains all the status bits that the DMA reports to the application. The

ETH_DMASR register is usually read by the software driver during an interrupt service

routine or polling. Most of the fields in this register cause the host to be interrupted. The

ETH_DMASR register bits are not cleared when read. Writing 1 to (unreserved) bits in

ETH_DMASR register[16:0] clears them and writing 0 has no effect. Each field (bits [16:0])

can be masked by masking the appropriate bit in the ETH_DMAIER register.

Bits 31:0 STL: Start of transmit list

This field contains the base address of the first descriptor in the transmit descriptor list.

The LSB bits [1/2/3:0] for 32/64/128-bit bus width) are internally ignored and taken as all-

zero by the DMA. Hence these LSB bits are read-only.

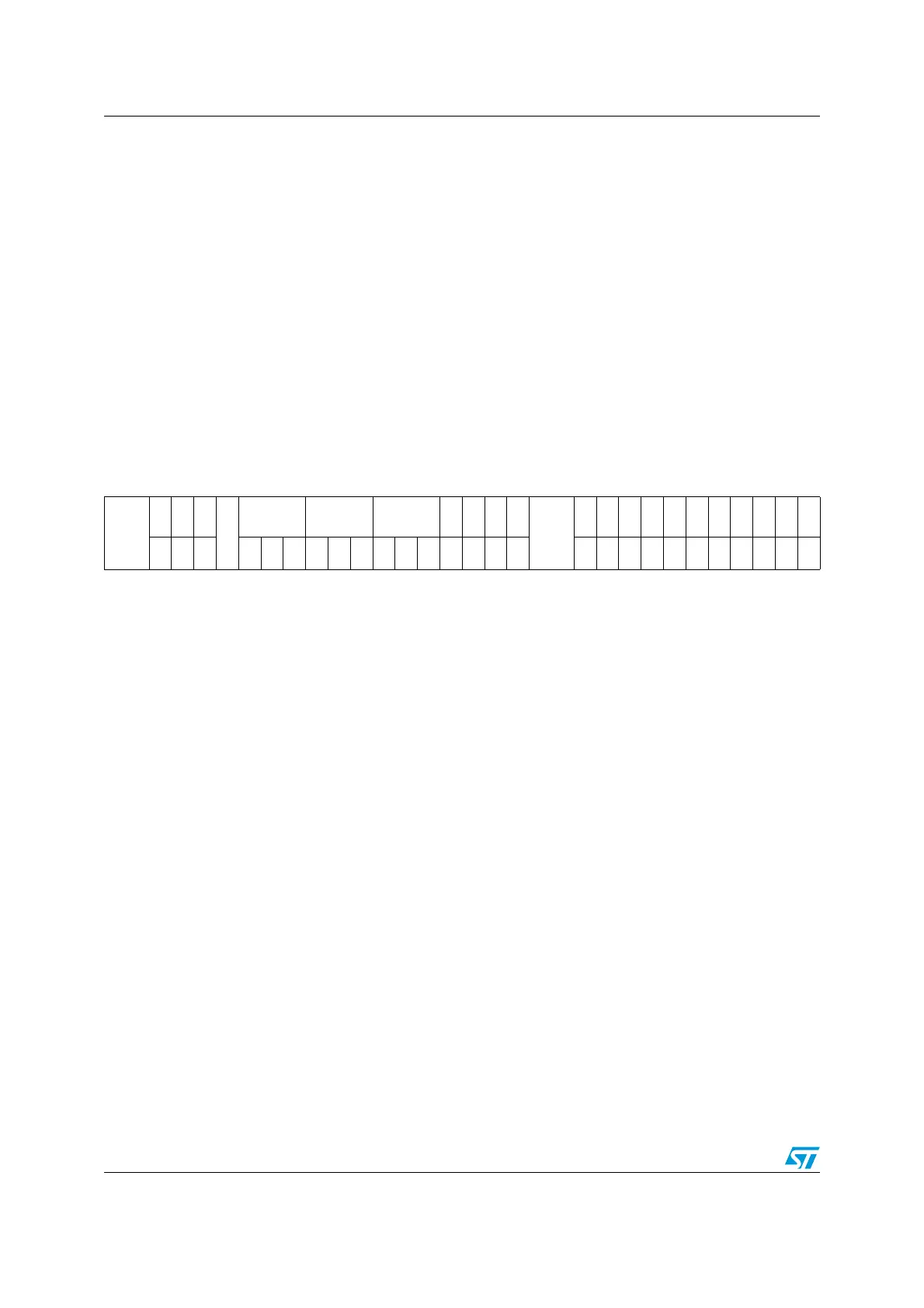

313029282726252423222120191817161514131211109876543210

Reserved

TSTS

PMTS

MMCS

Reserved

EBS

TPS

RPS

NIS

AIS

ERS

FBES

Reserved

ETS

RWTS

RPSS

RBUS

RS

TUS

ROS

TJTS

TBUS

TPSS

TS

rrr rrrrrrrrr

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

rc-

w1

Bits 31:30 Reserved, must be kept at reset value.

Bit 29 TSTS: Time stamp trigger status

This bit indicates an interrupt event in the MAC core's Time stamp generator block. The

software must read the MAC core’s status register, clearing its source (bit 9), to reset this bit

to 0. When this bit is high an interrupt is generated if enabled.

Bit 28 PMTS: PMT status

This bit indicates an event in the MAC core’s PMT. The software must read the

corresponding registers in the MAC core to get the exact cause of interrupt and clear its

source to reset this bit to 0. The interrupt is generated when this bit is high if enabled.

Bit 27 MMCS: MMC status

This bit reflects an event in the MMC of the MAC core. The software must read the

corresponding registers in the MAC core to get the exact cause of interrupt and clear the

source of interrupt to make this bit as 0. The interrupt is generated when this bit is high if

enabled.

Bit 26 Reserved, must be kept at reset value.

Bits 25:23 EBS: Error bits status

These bits indicate the type of error that caused a bus error (error response on the AHB

interface). Valid only with the fatal bus error bit (ETH_DMASR register [13]) set. This field

does not generate an interrupt.

Bit 23 1 Error during data transfer by TxDMA

0 Error during data transfer by RxDMA

Bit 24 1 Error during read transfer

0 Error during write transfer

Bit 25 1 Error during descriptor access

0 Error during data buffer access

Loading...

Loading...