MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 151

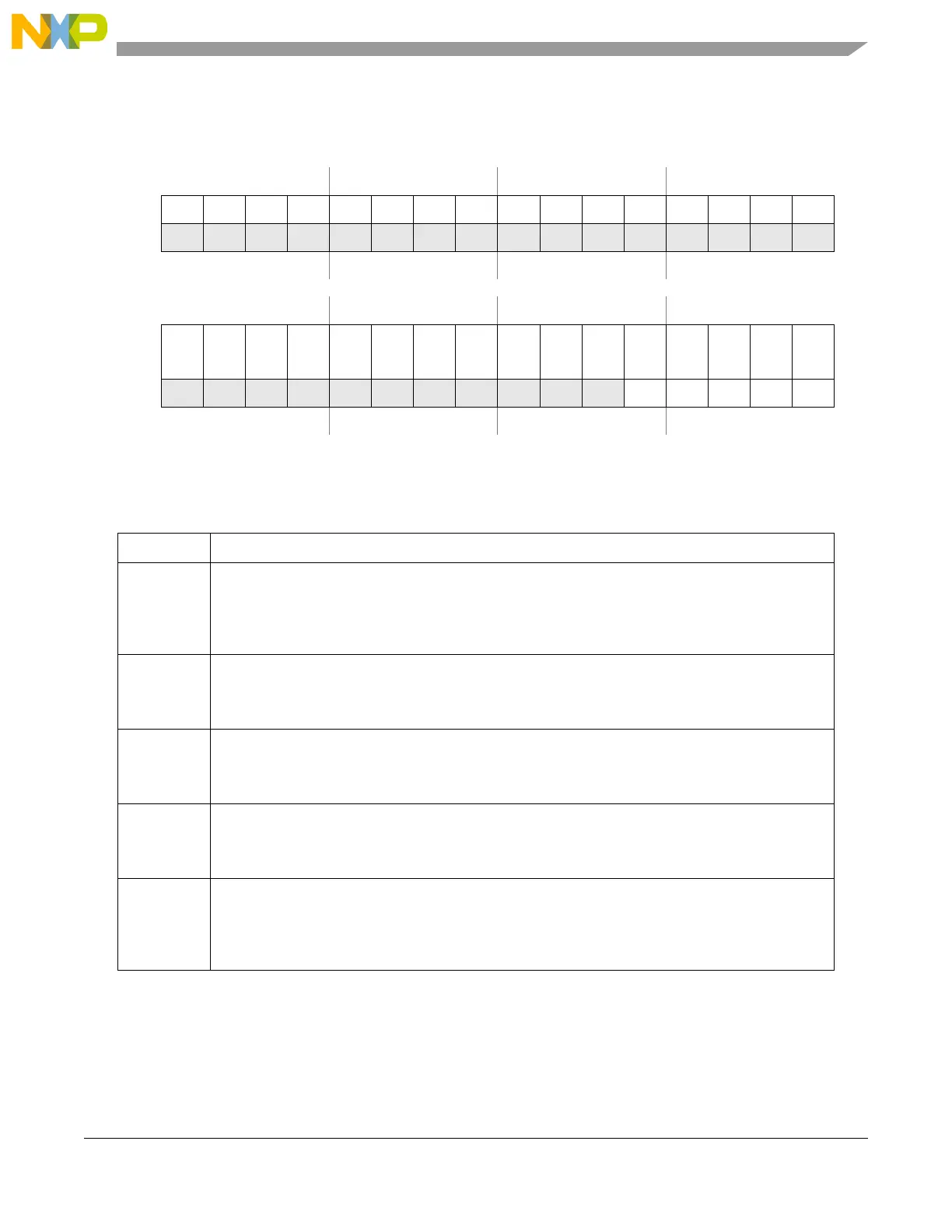

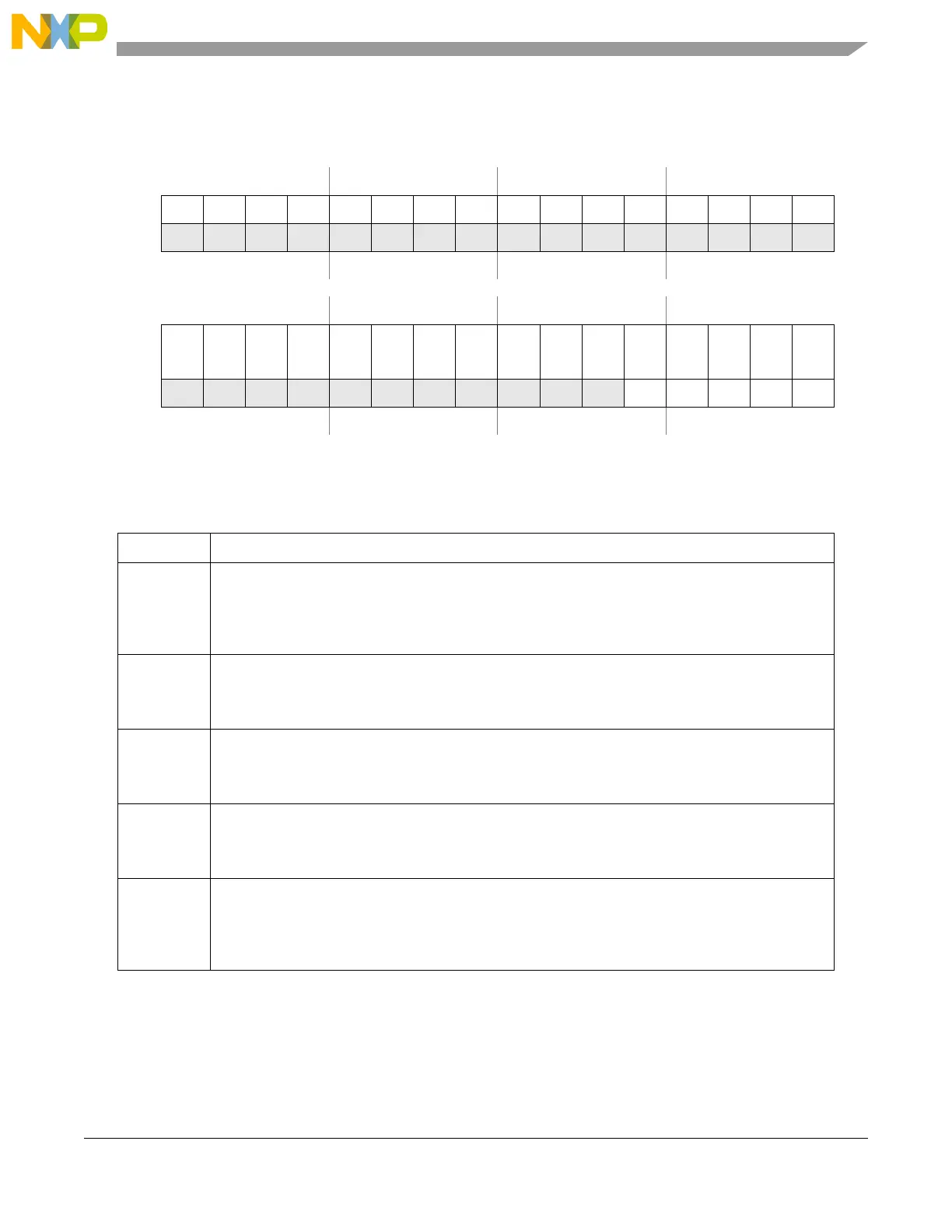

8.3.1.6 Invalid Mode Transition Status Register (ME_IMTS)

This register provides the status bits for each cause of invalid mode interrupt.

Address 0xC3FD_C014 Access: Supervisor read/write

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

00000000000

S_MTI

S_MRI

S_DMA

S_NMA

S_SEA

W w1c w1c w1c w1c w1c

Reset0000000000000000

Figure 8-7. Invalid Mode Transition Status Register (ME_IMTS)

Table 8-9. Invalid Mode Transition Status Register (ME_IMTS) Field Descriptions

Field Description

S_MTI Mode Transition Illegal status — This bit is set whenever a new mode is requested while some

other mode transition process is active (S_MTRANS is ‘1’). Please refer to Section 8.4.5, “Mode

Transition Interrupts for the exceptions to this behavior. It is cleared by writing a ‘1’ to this bit.

0 Mode transition requested is not illegal

1 Mode transition requested is illegal

S_MRI Mode Request Illegal status — This bit is set whenever the target mode requested is not a valid

mode with respect to current mode. It is cleared by writing a ‘1’ to this bit.

0 Target mode requested is not illegal with respect to current mode

1 Target mode requested is illegal with respect to current mode

S_DMA Disabled Mode Access status — This bit is set whenever the target mode requested is one of those

disabled modes determined by ME_ME register. It is cleared by writing a ‘1’ to this bit.

0 Target mode requested is not a disabled mode

1 Target mode requested is a disabled mode

S_NMA Non-existing Mode Access status — This bit is set whenever the target mode requested is one of

those non existing modes determined by ME_ME register. It is cleared by writing a ‘1’ to this bit.

0 Target mode requested is an existing mode

1 Target mode requested is a non-existing mode

S_SEA SAFE Event Active status — This bit is set whenever the device is in SAFE mode, SAFE event bit is

pending and a new mode requested other than RESET/SAFE modes. It is cleared by writing a ‘1’ to

this bit.

0 No new mode requested other than RESET/SAFE while SAFE event is pending

1 New mode requested other than RESET/SAFE while SAFE event is pending

Loading...

Loading...