MPC5604B/C Microcontroller Reference Manual, Rev. 8

178 Freescale Semiconductor

8.4.3.16 Power Domain #2 Switch-Off

Based on the device mode and the MC_PCU’s power configuration register PCU_PCONF2, the power

domain #2 is controlled by the MC_PCU.

If a mode change translates to a power-down of the power domain, then the MC_PCU starts the

power-down sequence. The MC_PCU acknowledges the completion of the power-down sequence with

respect to the new mode, and the MC_ME uses this information to update the mode transition status. This

step is executed only after the Peripheral Clocks Disable process has completed.

8.4.3.17 Pad Switch-Off

If the PDO bit of the ME_<target mode>_MC register is ‘1’ then

• the outputs of the pads are forced to the high impedance state if the target mode is SAFE or TEST

• I/O pads power sequence driver is switched off if the target mode is one of SAFE, TEST, or STOP

modes

In STANDBY mode, the power sequence driver and all pads except the external reset and those mapped

on wakeup lines are not powered and therefore high impedance. The wakeup line configuration remains

unchanged.

This step is executed only after the Peripheral Clocks Disable process is completed.

8.4.3.18 FMPLL Switch-Off

Based on the FMPLLON bit of the ME_<current mode>_MC and ME_<target mode>_MC registers, if

FMPLL is to be switched off, the MC_ME requests the FMPLL to power down and updates its availability

status bit S_FMPLL of the ME_GS register to ‘0’. This step is executed only after the System Clock

Switching process is completed.

4-16 MHz

ext. xtal

osc.

div. ext.

xtal osc.

freq. mod.

PLL

system

clock is

disabled

(default)

1

disabling the system clock during TEST mode will require a reset in order to exit TEST mode

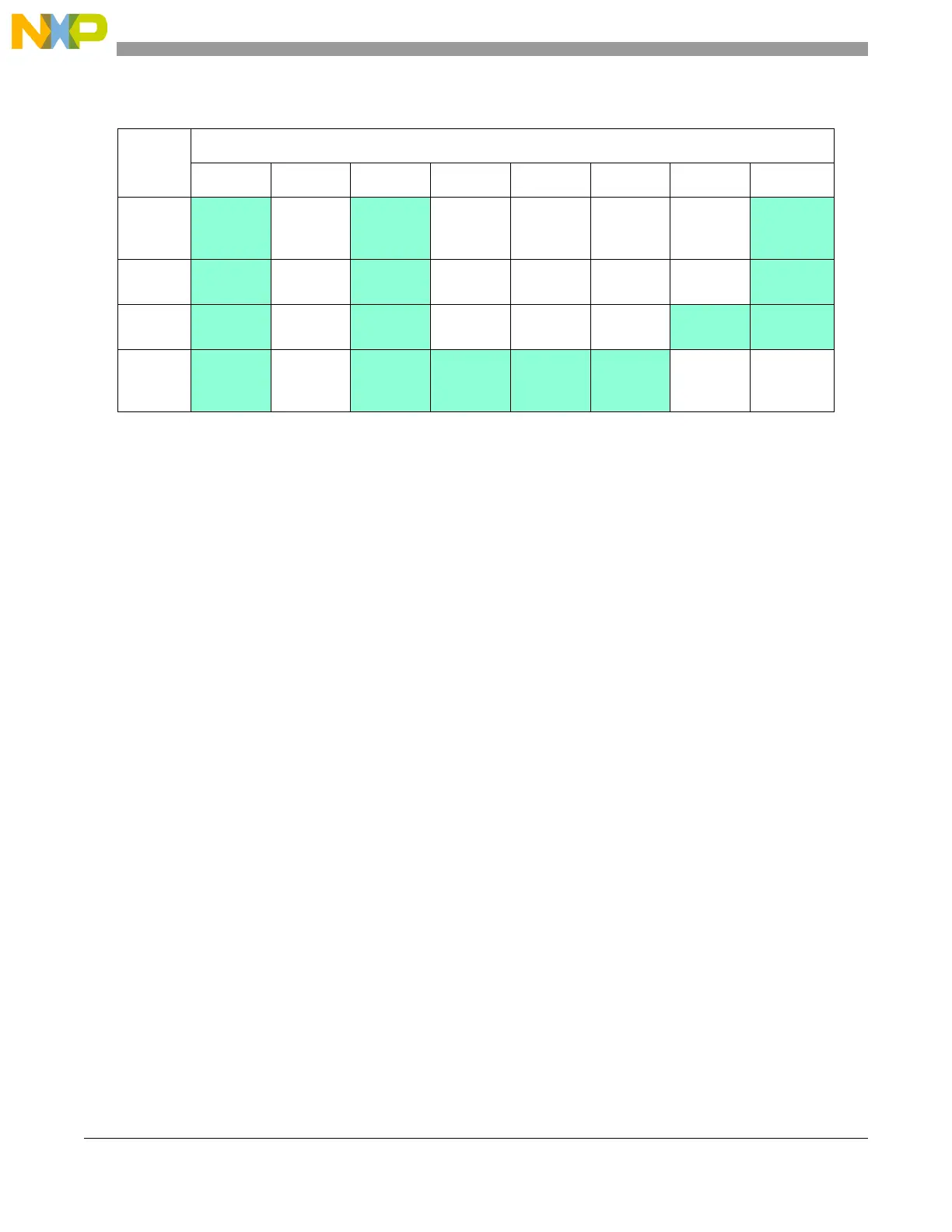

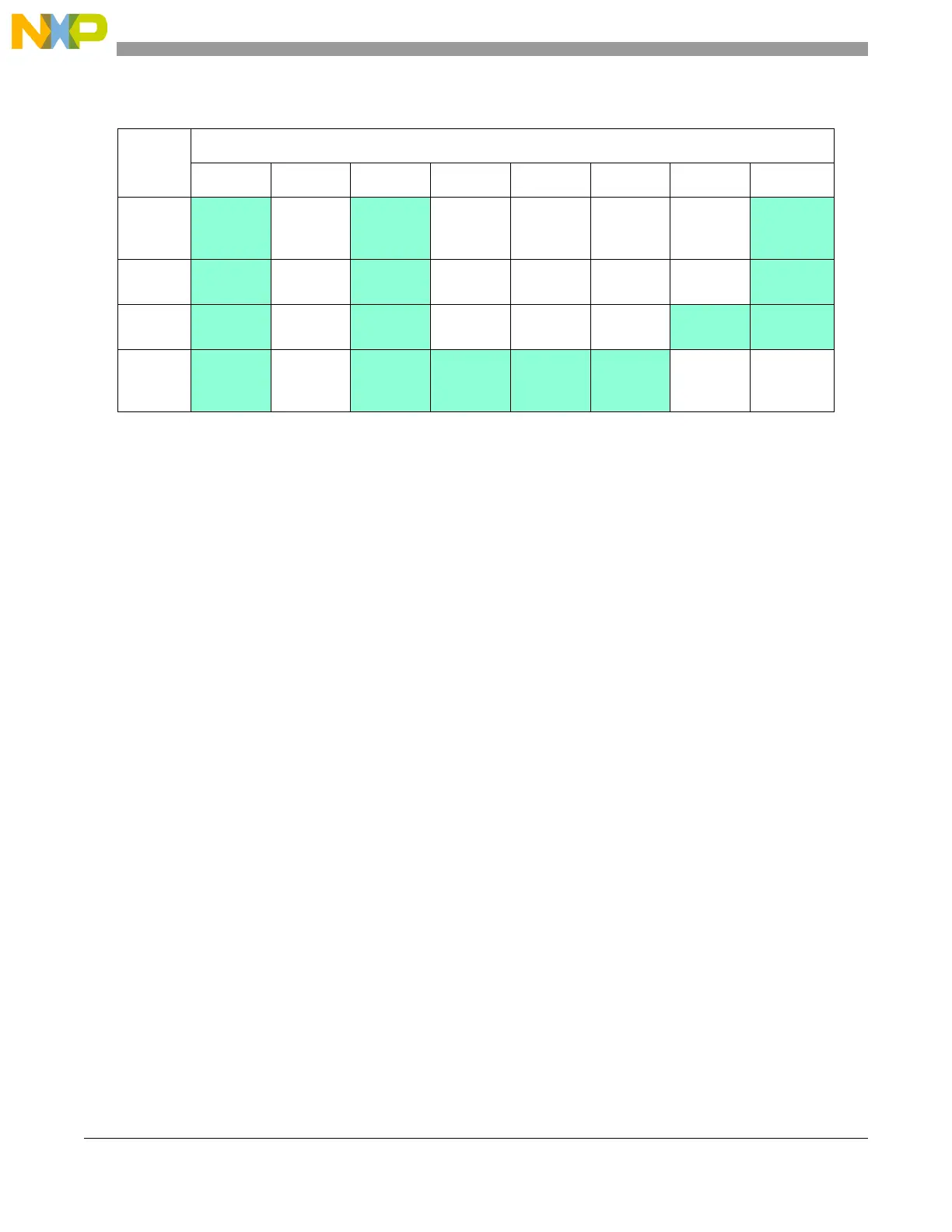

Table 8-18. MC_ME System Clock Selection Overview (continued)

System

Clock

Source

Mode

RESET TEST SAFE DRUN RUN0…3 HALT STOP STANDBY

Loading...

Loading...