MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 177

• The target clock configuration for the 16 MHz int. RC osc. is effective only when the S_FIRC bit

of the ME_GS register is set by hardware (i.e. the fast internal RC oscillator (16 MHz) has

stabilized).

• The target clock configuration for the div. 16 MHz int. RC osc. is effective only when the S_FIRC

bit of the ME_GS register is set by hardware (i.e. the fast internal RC oscillator (16 MHz) has

stabilized).

• The target clock configuration for the 4-16 MHz ext. xtal osc. is effective only when the S_FXOSC

bit of the ME_GS register is set by hardware (i.e the fast external crystal oscillator (4-16 MHz) has

stabilized).

• The target clock configuration for the div. ext. xtal osc. is effective only when the S_FXOSC bit of

the ME_GS register is set by hardware (i.e the fast external crystal oscillator (4-16 MHz) has

stabilized).

• The target clock configuration for the freq. mod. PLL is effective only when the S_FMPLL bit of

the ME_GS register is set by hardware (i.e. the frequency modulated phase locked loop has

stabilized).

• If the clock is to be disabled, the SYSCLK bit field should be programmed with “1111”. This is

possible only in the STOP and TEST modes. In the STANDBY mode, the clock configuration is

fixed, and the system clock is automatically forced to ‘0’.

The current system clock configuration can be observed by reading the S_SYSCLK bit field of the ME_GS

register, which is updated after every system clock switching. Until the target clock is available, the system

uses the previous clock configuration.

System clock switching starts only after

• the Clock Sources Switch-On process has completed if the target system clock source needs to be

switched on

• the FMPLL Switch-On process has completed if the target system clock is the freq. mod. PLL

• the Peripheral Clocks Disable process is completed in order not to change the system clock

frequency before peripherals close their internal activities

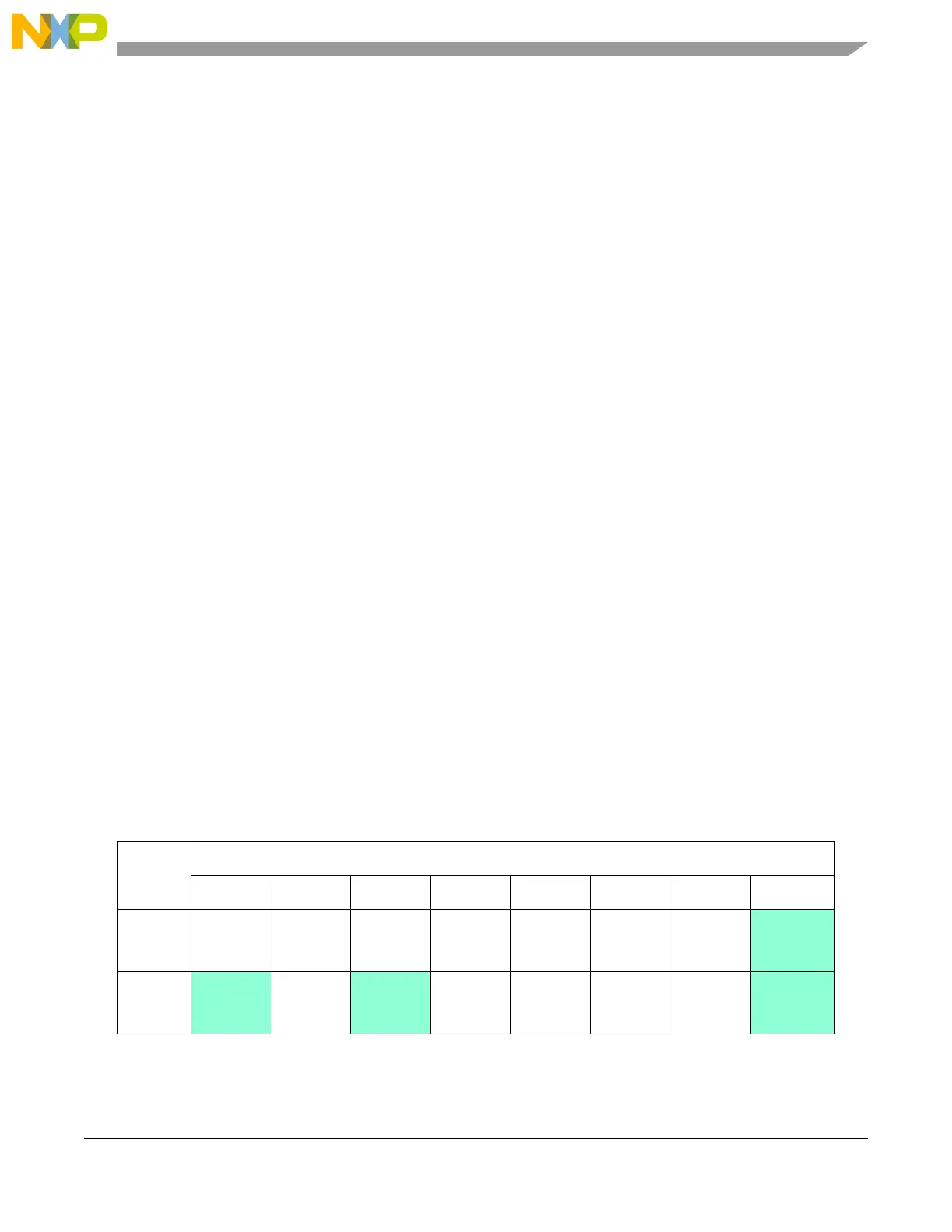

An overview of system clock source selection possibilities for each mode is shown in Table 8-18. A ‘’

indicates that a given clock source is selectable for a given mode.

Table 8-18. MC_ME System Clock Selection Overview

System

Clock

Source

Mode

RESET TEST SAFE DRUN RUN0…3 HALT STOP STANDBY

16 MHz

int. RC

osc.

(default)

(default)

(default)

(default)

(default)

(default)

(default)

div. 16

MHz int.

RC osc.

Loading...

Loading...