MPC5604B/C Microcontroller Reference Manual, Rev. 8

400 Freescale Semiconductor

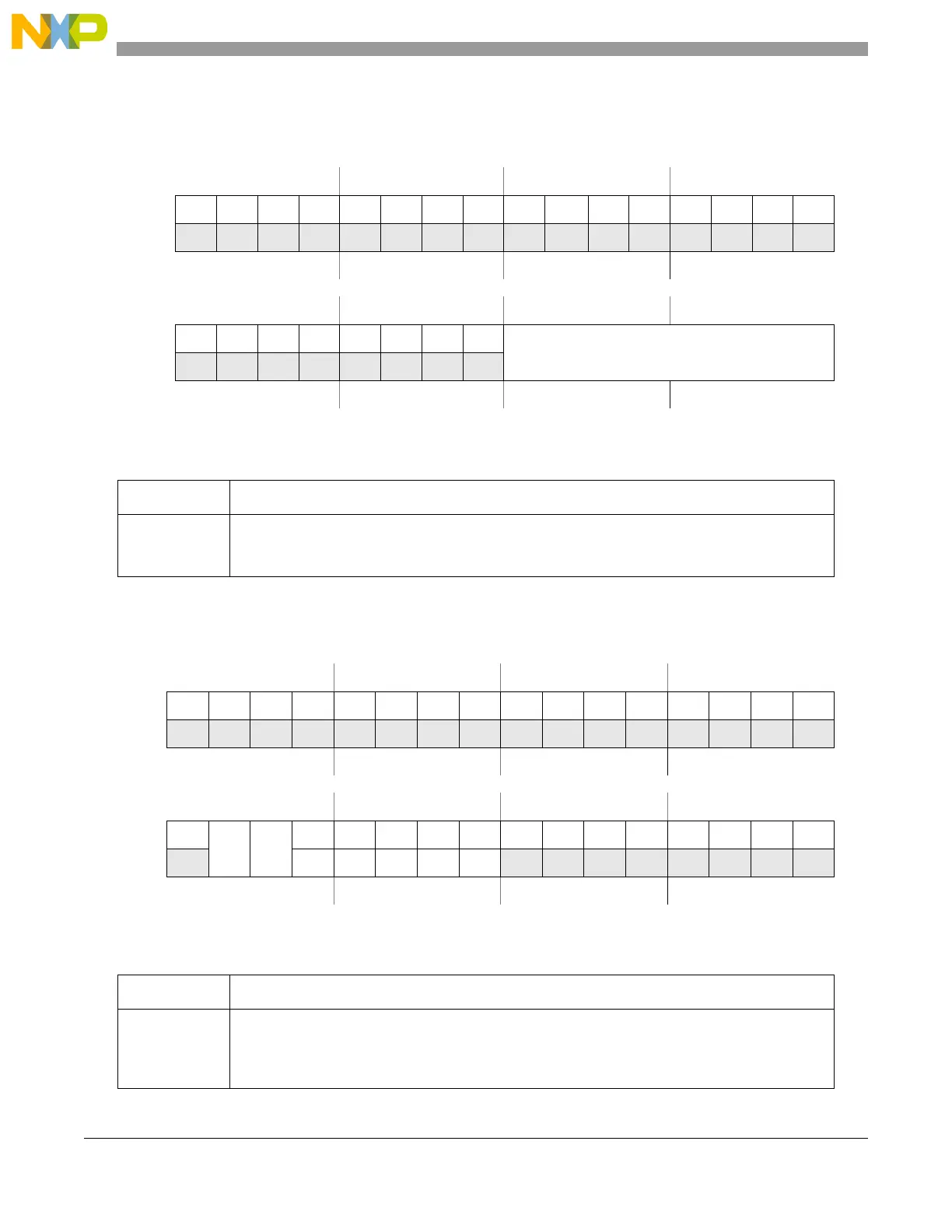

21.7.1.12 LIN checksum field register (LINCFR)

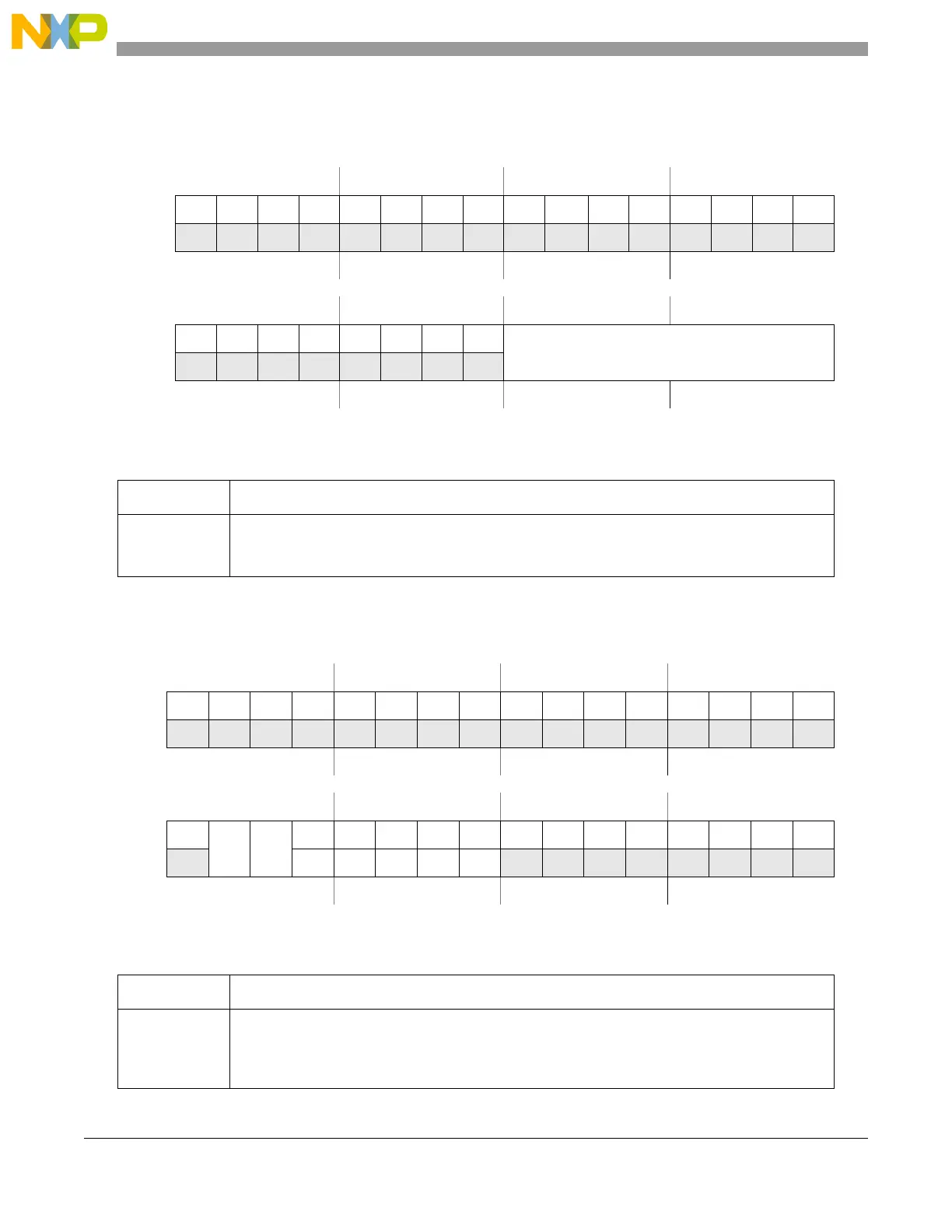

21.7.1.13 LIN control register 2 (LINCR2)

Offset: 0x002C Access: User read/write

0123456789101112131415

R 0000000000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 00000000

CF

W

Reset0000000000000000

Figure 21-17. LIN checksum field register (LINCFR)

Table 21-18. LINCFR field descriptions

Field Description

CF Checksum bits

When LINCR1[CCD] = 0, this field is read-only. When LINCR1[CCD] = 1, this field is read/write.

See Table 21-4.

Offset: 0x0030 Access: User read/write

0123456789101112131415

R 0000000000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0

IOBE IOPE

0 0 0 0 0 0 0 0 0 0 0 0 0

W

WURQ

DDRQ

DTRQ ABRQ HTRQ

Reset0110000000000000

Figure 21-18. LIN control register 2 (LINCR2)

Table 21-19. LINCR2 field descriptions

Field Description

IOBE Idle on Bit Error

0 Bit error does not reset LIN state machine.

1 Bit error reset LIN state machine.

This bit can be set/cleared in Initialization mode only.

Loading...

Loading...