MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 437

22.3.4.2 Control Register (CTRL)

This register is defined for specific FlexCAN control features related to the CAN bus, such as bit-rate,

programmable sampling point within an Rx bit, Loop-Back Mode, Listen-Only Mode, Bus Off recovery

behavior and interrupt enabling (Bus-Off, Error, Warning). It also determines the Division Factor for the

clock prescaler. This register can be accessed at any time, however some fields must be changed only

during either Disable Mode or Freeze Mode. Find more information in the fields descriptions ahead.

IDAM ID Acceptance Mode

This 2-bit field identifies the format of the elements of the Rx FIFO filter table, as shown in

Tabl e 22-9. Note that all elements of the table are configured at the same time by this field (they are

all the same format). See Section 22.3.3, “Rx FIFO structure. This bit must be written in Freeze

mode only.

MAXMB Maximum Number of Message Buffers

This 6-bit field defines the maximum number of message buffers that will take part in the matching

and arbitration processes. The reset value (0x0F) is equivalent to 16 MB configuration. This field

must be changed only while the module is in Freeze Mode.

Maximum MBs in use = MAXMB + 1

Note: MAXMB must be programmed with a value smaller or equal to the number of available

Message Buffers, otherwise FlexCAN can transmit and receive wrong messages.

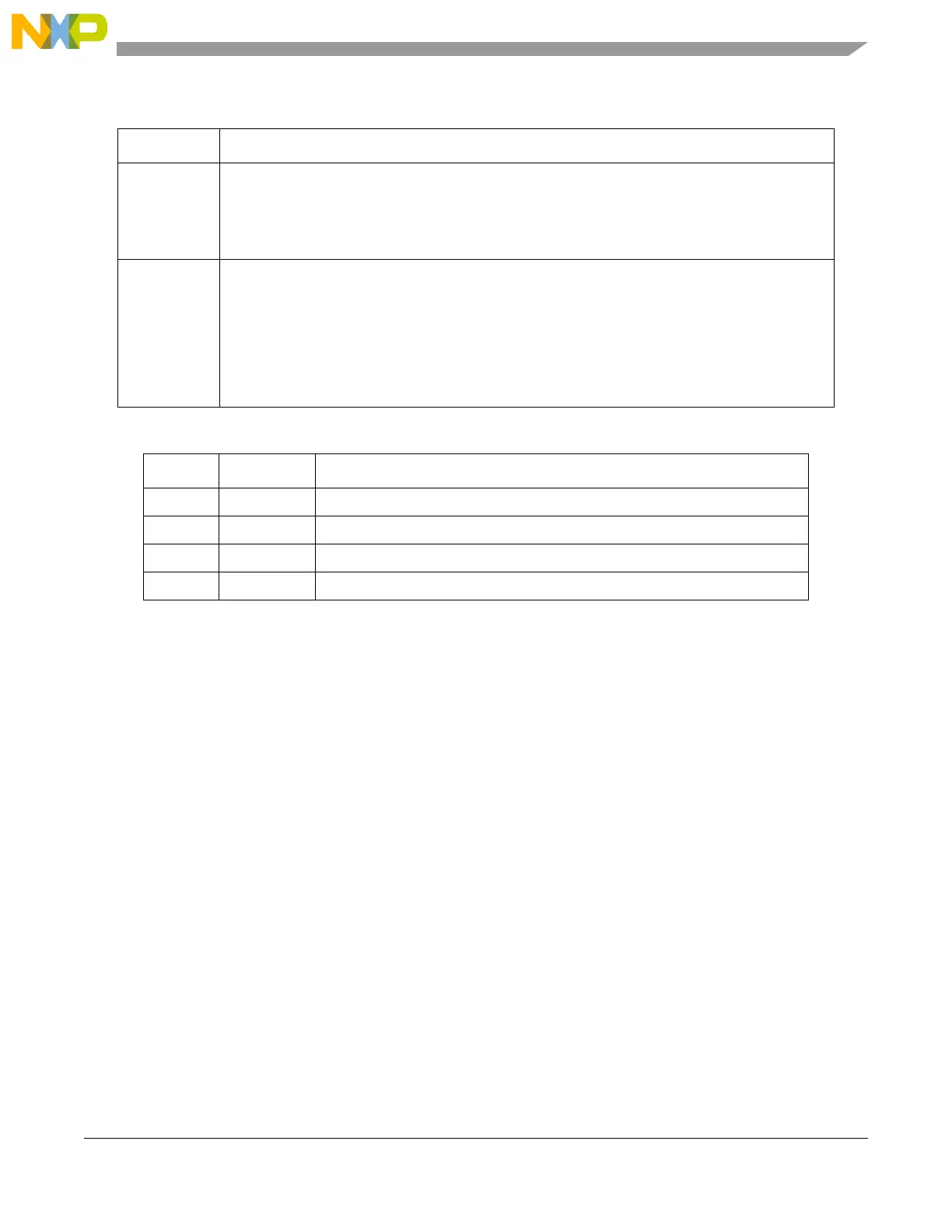

Table 22-9. IDAM coding

IDAM Format Explanation

00 A One full ID (standard or extended) per filter element

01 B Two full standard IDs or two partial 14-bit extended IDs per filter element

10 C Four partial 8-bit IDs (standard or extended) per filter element

11 D All frames rejected

Table 22-8. MCR field descriptions (continued)

Field Description

Loading...

Loading...