MPC5604B/C Microcontroller Reference Manual, Rev. 8

438 Freescale Semiconductor

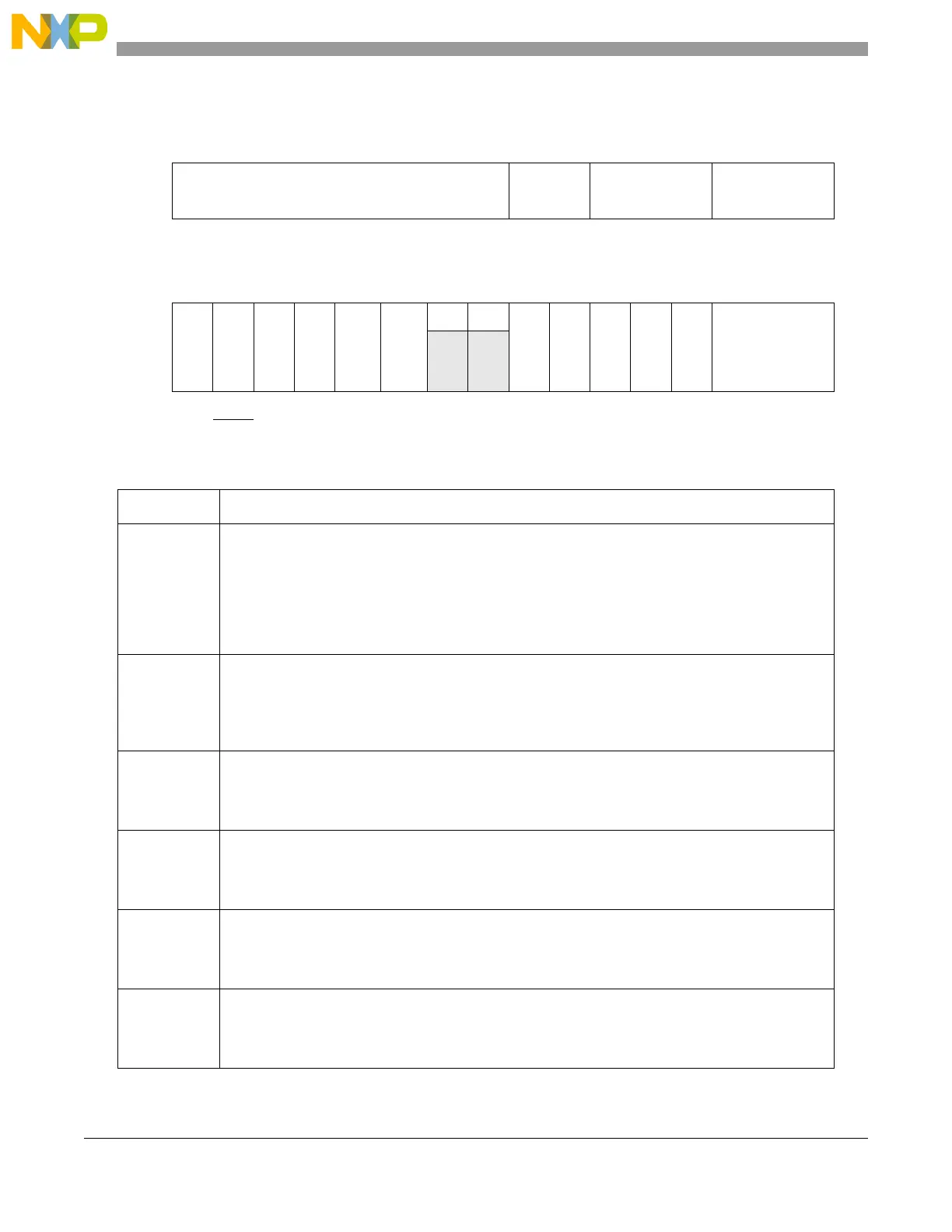

Offset: 0x0004 Access: Read/write

0123 4 5 6789101112131415

R

PRESDIV RJW PSEG1 PSEG2

W

Reset0000 0 0 0000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

BOFF_MSK

ERR_ MSK

CLK_SRC

LPB

TWRN_MSK

RWRN_MSK

00

SMP

BOFF_REC

TSYN

LBUF

LOM PROPSEG

W

Reset0000 0 0 0000000000

Figure 22-6. Control Register (CTRL)

Table 22-10. CTRL field descriptions

Field Description

PRESDIV Prescaler Division Factor

This field defines the ratio between the CPI clock frequency and the Serial Clock (Sclock) frequency.

The Sclock period defines the time quantum of the CAN protocol. For the reset value, the Sclock

frequency is equal to the CPI clock frequency. The Maximum value of this register is 0xFF, that gives

a minimum Sclock frequency equal to the CPI clock frequency divided by 256. For more information

refer to Section 22.4.9.4, “Protocol timing. This bit must be written in Freeze mode only.

Sclock frequency = CPI clock frequency / (PRESDIV + 1)

RJW Resync Jump Width

This field defines the maximum number of time quanta

1

that a bit time can be changed by one

resynchronization. The valid programmable values are 0–3. This bit must be written in Freeze mode

only.

Resync Jump Width = RJW + 1.

PSEG1 PSEG1 — Phase Segment 1

This field defines the length of Phase Buffer Segment 1 in the bit time. The valid programmable

values are 0–7. This bit must be written in Freeze mode only.

Phase Buffer Segment 1 = (PSEG1 + 1) x Time-Quanta.

PSEG2 PSEG2 — Phase Segment 2

This field defines the length of Phase Buffer Segment 2 in the bit time. The valid programmable

values are 1–7. This bit must be written in Freeze mode only.

Phase Buffer Segment 2 = (PSEG2 + 1) x Time-Quanta.

BOFF_MSK Bus Off Mask

This bit provides a mask for the Bus Off Interrupt.

1= Bus Off interrupt enabled

0 = Bus Off interrupt disabled

ERR_MSK Error Mask

This bit provides a mask for the Error Interrupt.

1 = Error interrupt enabled

0 = Error interrupt disabled

Loading...

Loading...