MPC5604B/C Microcontroller Reference Manual, Rev. 8

448 Freescale Semiconductor

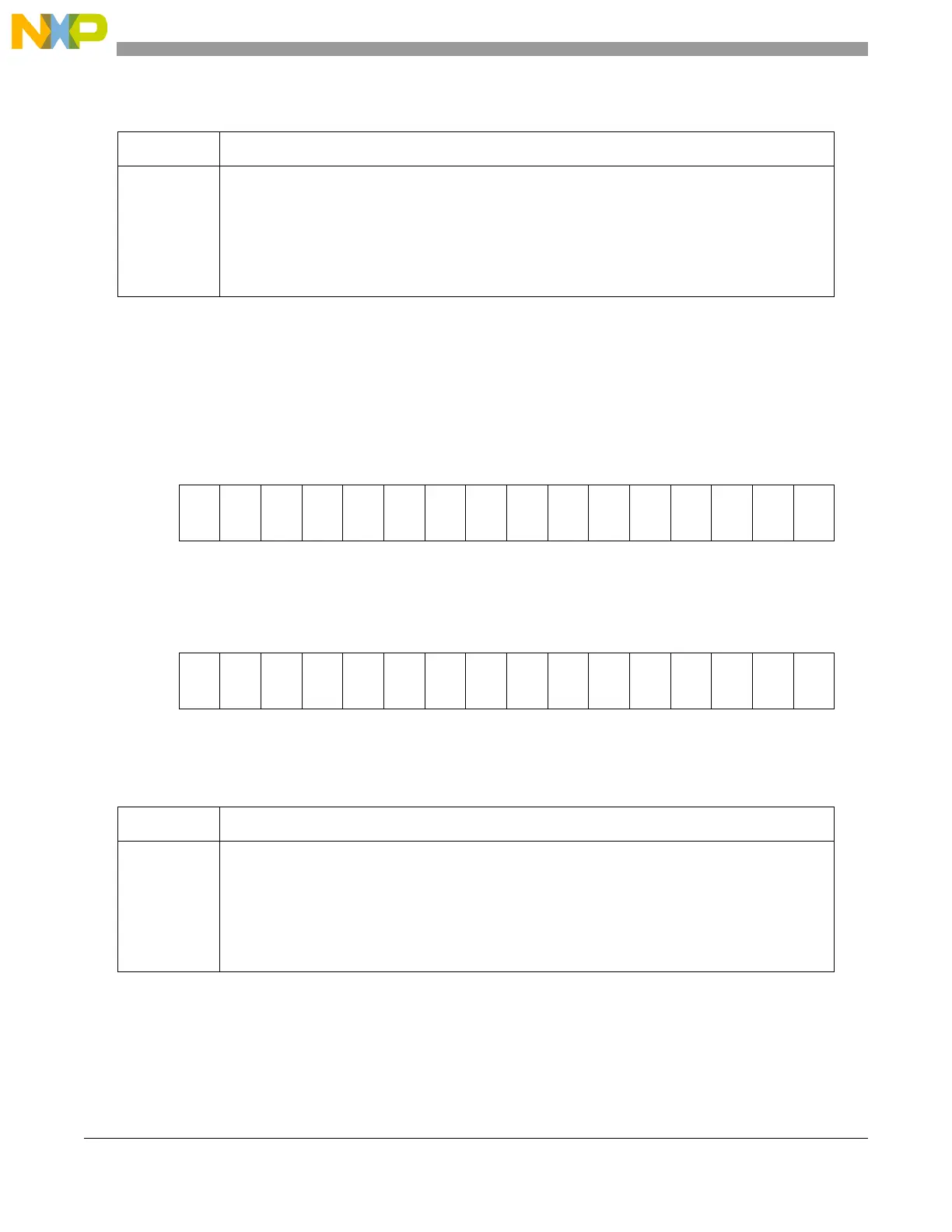

22.3.4.10 Interrupt Masks 1 Register (IMASK1)

This register allows to enable or disable any number of a range of 32 Message Buffer Interrupts. It contains

one interrupt mask bit per buffer, enabling the CPU to determine which buffer generates an interrupt after

a successful transmission or reception (i.e., when the corresponding IFLAG1 bit is set).

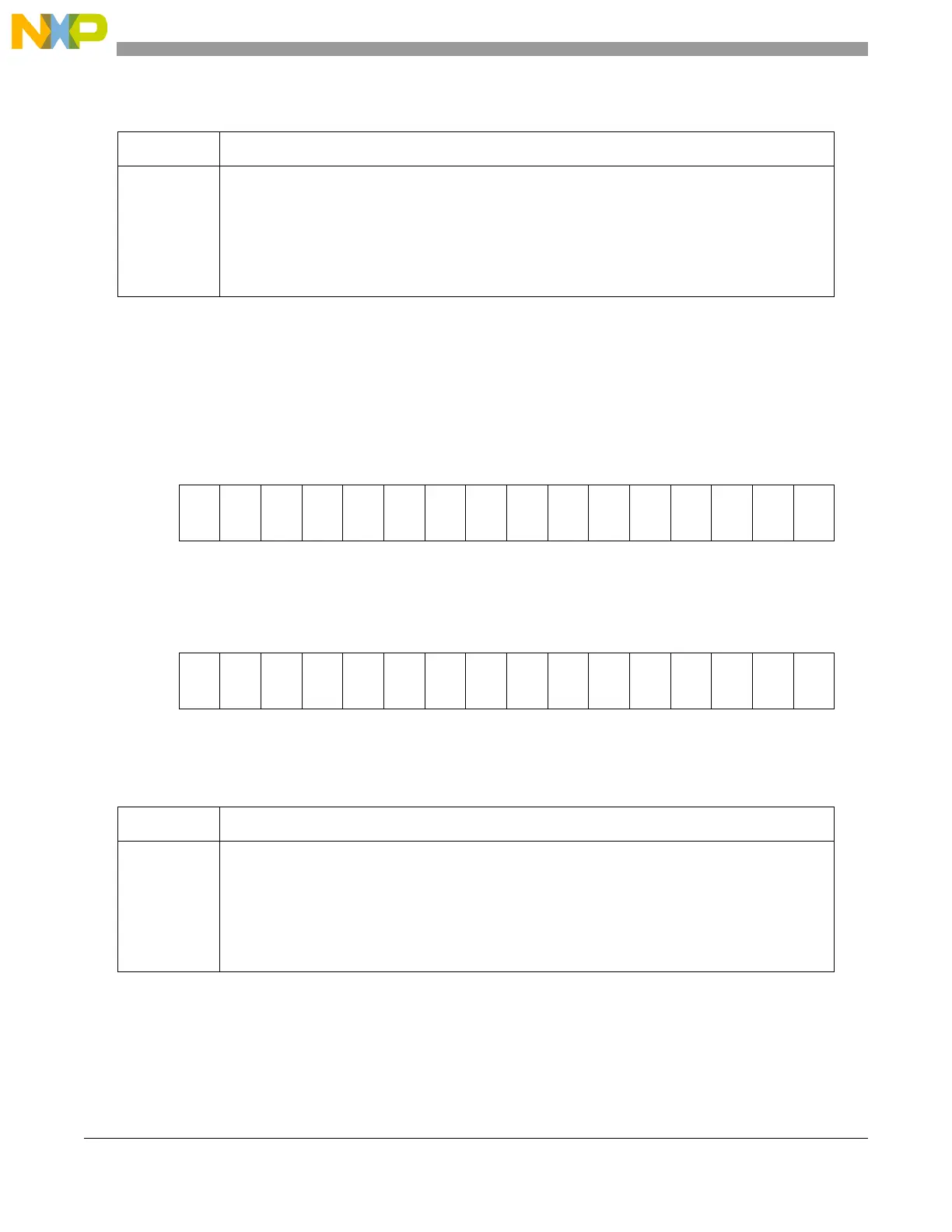

22.3.4.11 Interrupt Flags 2 Register (IFLAG2)

This register defines the flags for 32 Message Buffer interrupts. It contains one interrupt flag bit per buffer.

Each successful transmission or reception sets the corresponding IFLAG2 bit. If the corresponding

Table 22-14. IMASK2 field descriptions

Field Description

BUF63M –

BUF32M

Buffer MB

i

Mask

Each bit enables or disables the respective FlexCAN Message Buffer (MB32 to MB63) Interrupt.

1 = The corresponding buffer Interrupt is enabled

0 = The corresponding buffer Interrupt is disabled

Note: Setting or clearing a bit in the IMASK2 Register can assert or negate an interrupt request, if

the corresponding IFLAG2 bit is set.

Offset: 0x0028 Access: Read/write

0123456789101112131415

R

BUF

31M

BUF

30M

BUF

29M

BUF

28M

BUF

27M

BUF

26M

BUF

25M

BUF

24M

BUF

23M

BUF

22M

BUF

21M

BUF

20M

BUF

19M

BUF

18M

BUF

17M

BUF

16M

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

BUF

15M

BUF

14M

BUF

13M

BUF

12M

BUF

11M

BUF

10M

BUF

9M

BUF

8M

BUF

7M

BUF

6M

BUF

5M

BUF

4M

BUF

3M

BUF

2M

BUF

1M

BUF

0M

W

Reset0000000000000000

Figure 22-12. Interrupt Masks 1 Register (IMASK1)

Table 22-15. IMASK1 field descriptions

Field Description

BUF31M –

BUF0M

BUF31M–BUF0M — Buffer MB

i

Mask

Each bit enables or disables the respective FlexCAN Message Buffer (MB0 to MB31) Interrupt.

1 = The corresponding buffer Interrupt is enabled

0 = The corresponding buffer Interrupt is disabled

Note: Setting or clearing a bit in the IMASK1 Register can assert or negate an interrupt request, if

the corresponding IFLAG1 bit is set.

Loading...

Loading...