MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 449

IMASK2 bit is set, an interrupt will be generated. The interrupt flag must be cleared by writing it to ‘1’.

Writing ‘0’ has no effect.

When the AEN bit in the MCR is set (Abort enabled), while the IFLAG2 bit is set for a MB configured as

Tx, the writing access done by CPU into the corresponding MB will be blocked.

22.3.4.12 Interrupt Flags 1 Register (IFLAG1)

This register defines the flags for 32 Message Buffer interrupts and FIFO interrupts. It contains one

interrupt flag bit per buffer. Each successful transmission or reception sets the corresponding IFLAG1 bit.

If the corresponding IMASK1 bit is set, an interrupt will be generated. The Interrupt flag must be cleared

by writing it to ‘1’. Writing ‘0’ has no effect.

When the AEN bit in the MCR is set (Abort enabled), while the IFLAG1 bit is set for a MB configured as

Tx, the writing access done by CPU into the corresponding MB will be blocked.

When the FEN bit in the MCR is set (FIFO enabled), the function of the 8 least significant interrupt flags

(BUF7I – BUF0I) is changed to support the FIFO operation. BUF7I, BUF6I and BUF5I indicate operating

conditions of the FIFO, while BUF4I to BUF0I are not used.

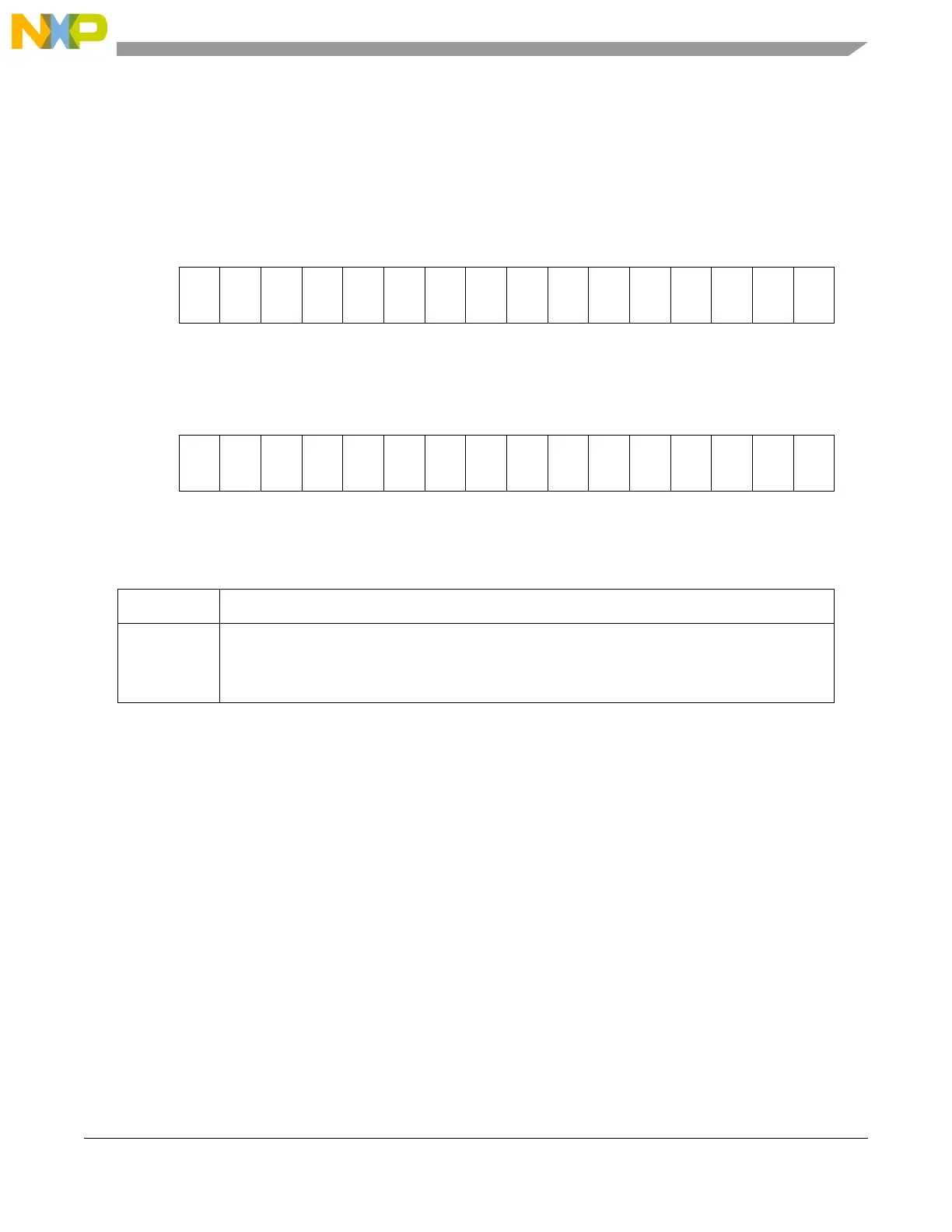

Offset: 0x002C Access: Read/write

0123456789101112131415

R

BUF

63I

BUF

62I

BUF

61I

BUF

60I

BUF

59I

BUF

58I

BUF

57I

BUF

56I

BUF

55I

BUF

54I

BUF

53I

BUF

52I

BUF

51I

BUF

50I

BUF

49I

BUF

48I

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

BUF

47I

BUF

46I

BUF

45I

BUF

44I

BUF

43I

BUF

42I

BUF

41I

BUF

40I

BUF

39I

BUF

38I

BUF

37I

BUF

36I

BUF

35I

BUF

34I

BUF

33I

BUF

32I

W

Reset0000000000000000

Figure 22-13. Interrupt Flags 2 Register (IFLAG2)

Table 22-16. IFLAG2 field descriptions

Field Description

BUF32I –

BUF63I

Buffer MB

i

Interrupt

Each bit flags the respective FlexCAN Message Buffer (MB32 to MB63) interrupt.

1 = The corresponding buffer has successfully completed transmission or reception

0 = No such occurrence

Loading...

Loading...