MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 463

NOTE

It is the user’s responsibility to ensure the bit time settings are in compliance

with the CAN standard. For bit time calculations, use an IPT (Information

Processing Time) of 2, which is the value implemented in the FlexCAN

module.

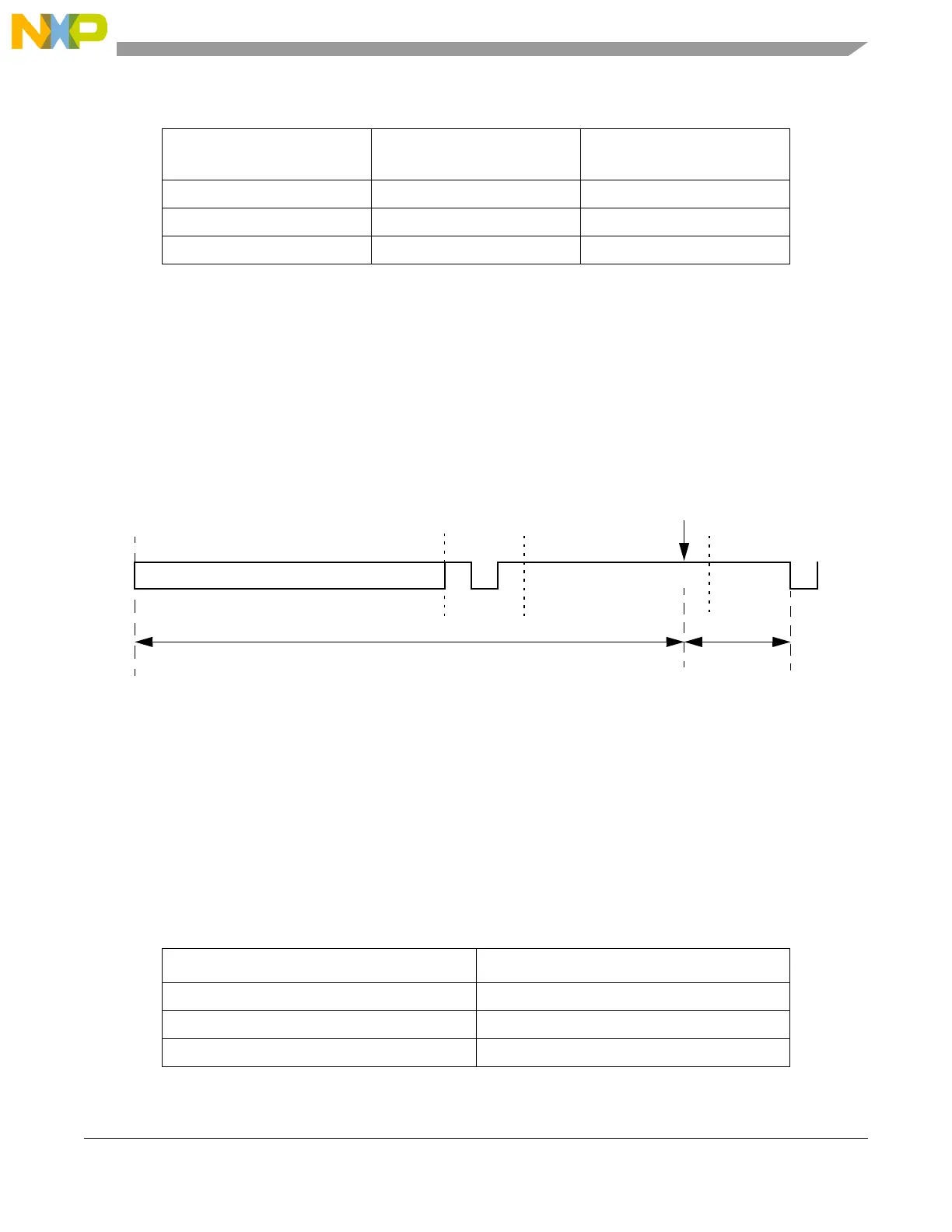

22.4.9.5 Arbitration and matching timing

During normal transmission or reception of frames, the arbitration, matching, move-in and move-out

processes are executed during certain time windows inside the CAN frame, as shown in Figure 22-18.

Figure 22-18. Arbitration, match and move time windows

When doing matching and arbitration, FlexCAN needs to scan the whole Message Buffer memory during

the available time slot. In order to have sufficient time to do that, the following requirements must be

observed:

• A valid CAN bit timing must be programmed, as indicated in Table 22-20

• The peripheral clock frequency cannot be smaller than the oscillator clock frequency, i.e. the

FMPLL cannot be programmed to divide down the oscillator clock

• There must be a minimum ratio between the peripheral clock frequency and the CAN bit rate, as

specified in Table 22-21

7 .. 14 6 1 .. 4

8 .. 15 7 1 .. 4

9 .. 16 8 1 .. 4

Table 22-21. Minimum ratio between peripheral clock frequency and CAN bit rate

Number of message buffers Minimum ratio

16 8

32 8

64 16

Table 22-20. CAN standard compliant bit time segment settings (continued)

Time segment 1 Time segment 2

Resynchronization jump

width

CRC (15)

EOF (7)

Interm

Start Move

Matching/Arbitration Window (24 bits)

Move

(bit 6)

Window

Loading...

Loading...