MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 545

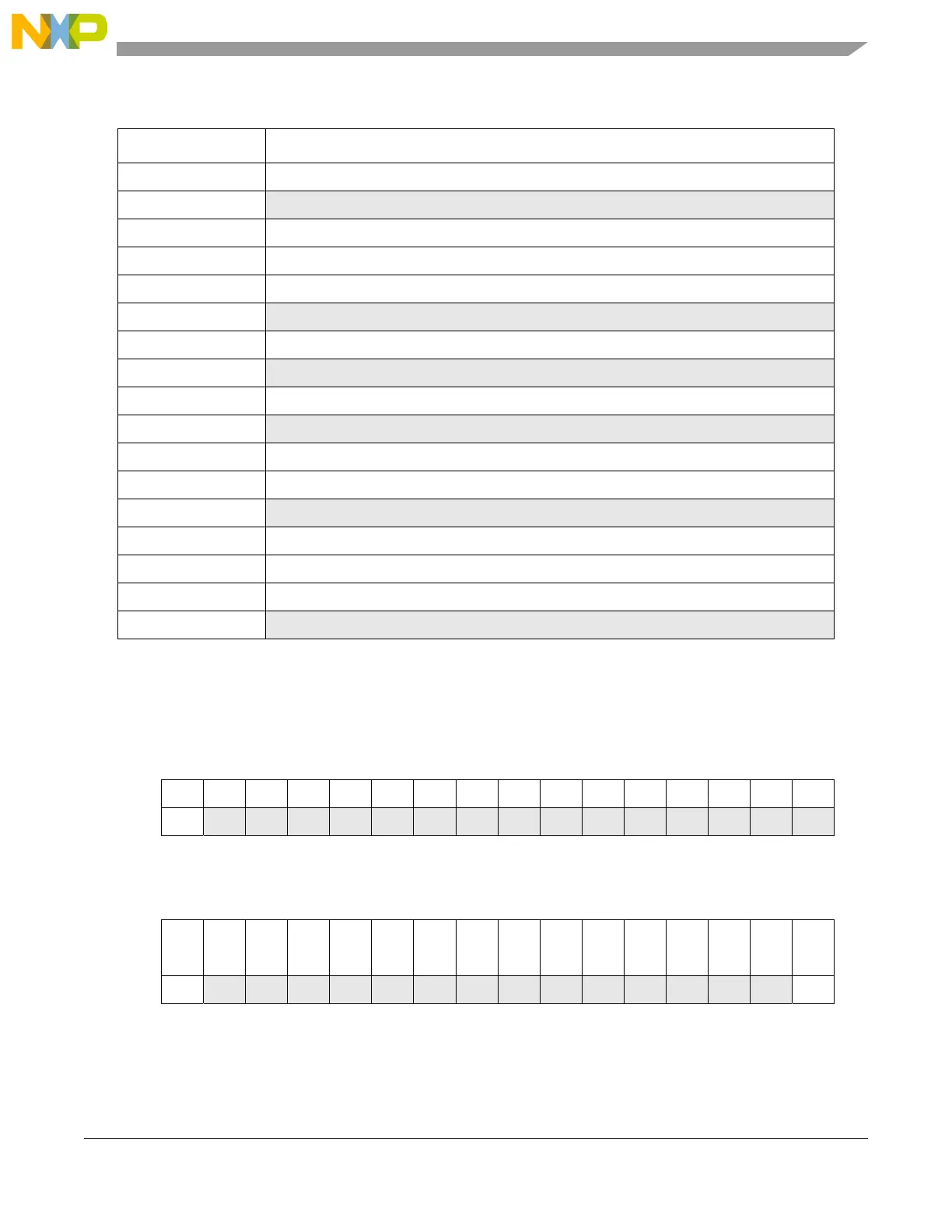

24.4.3.2.9 eMIOS UC Status Register (EMIOSS[n])

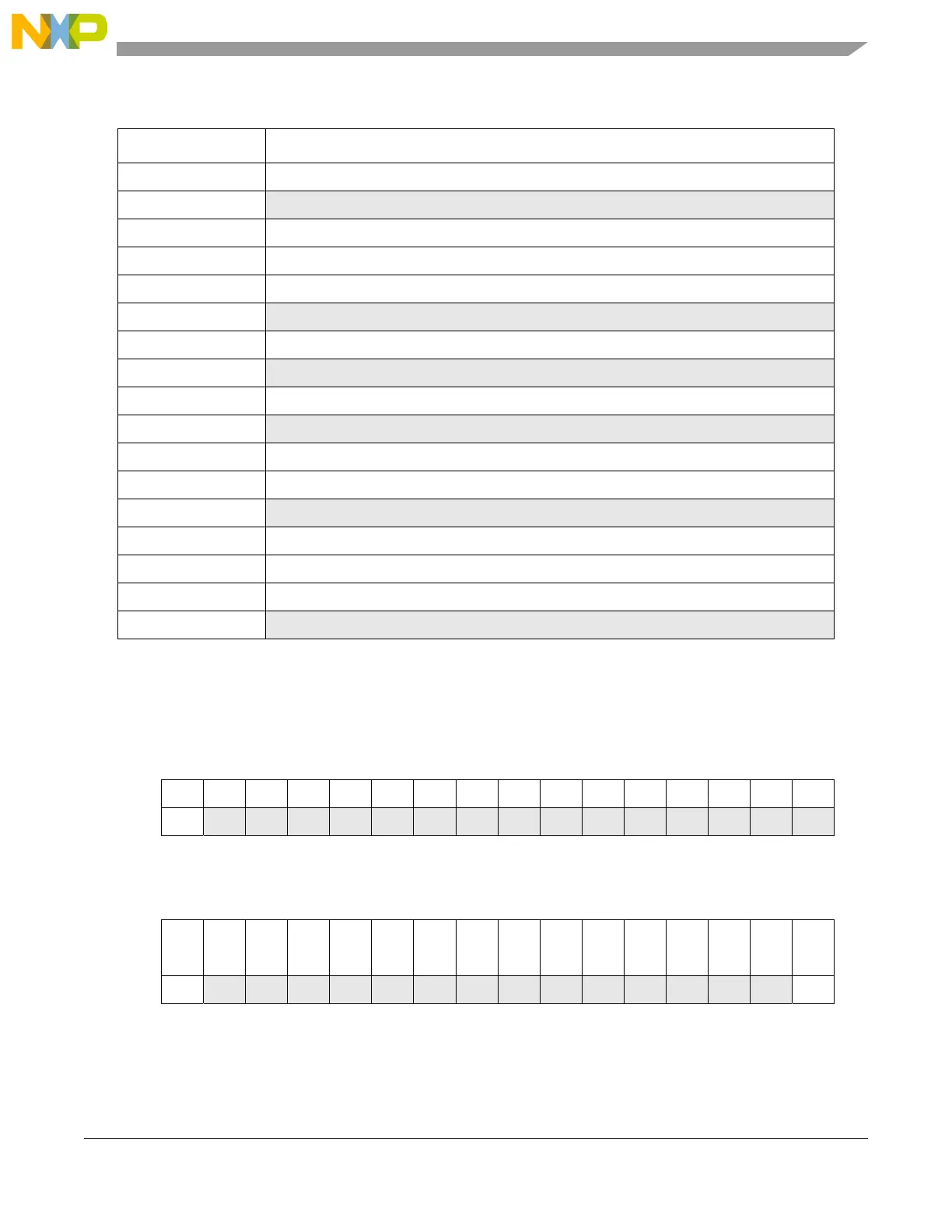

0000111 Double Action Output Compare (with FLAG set on both match)

0001000 – 0001111

Reserved

001000b Modulus Counter (Up counter with clear on match start)

001001b Modulus Counter (Up counter with clear on match end)

00101bb Modulus Counter (Up/Down counter)

0011000 – 0100101 Reserved

0100110 Output Pulse Width Modulation with Trigger

0100111 – 1001111 Reserved

101000b Modulus Counter Buffered (Up counter)

101001b Reserved

10101bb Modulus Counter Buffered (Up/Down counter)

10110b0 Output Pulse Width and Frequency Modulation Buffered

10110b1 Reserved

10111b0 Center Aligned Output Pulse Width Modulation Buffered (with trail edge dead-time)

10111b1 Center Aligned Output Pulse Width Modulation Buffered (with lead edge dead-time)

11000b0 Output Pulse Width Modulation Buffered

1100001 – 1111111 Reserved

1

b = adjust parameters for the mode of operation. Refer to Section 24.4.4.1.1, UC modes of operation for details.

Address: UC[n] base address + 0x10

0123456789101112131415

ROVR000000000000000

Ww1c

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

OVFL

000000000000UCIN

UCOUT

FLAG

Ww1c w1c

Reset0000000000000000

Figure 24-16. eMIOS UC Status Register (EMIOSS[n])

Table 24-21. Channel mode selection (continued)

MODE

1

Mode of operation

Loading...

Loading...