MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 551

selected time base is latched into register A2 and, at the same time, the FLAG bit is set and the content of

register B2 is transferred to register B1 and to register A1.

If subsequent input capture events occur while the corresponding FLAG bit is set, registers A2, B1 and A1

will be updated with the latest captured values and the FLAG will remain set. Registers EMIOSA[n] and

EMIOSB[n] return the value in registers A2 and B1, respectively.

In order to guarantee coherent access, reading EMIOSA[n] forces B1 be updated with the content of

register A1. At the same time transfers between B2 and B1 are disabled until the next read of EMIOSB[n]

register. Reading EMIOSB[n] register forces B1 be updated with A1 register content and re-enables

transfers from B2 to B1, to take effect at the next trailing edge capture. Transfers from B2 to A1 are not

blocked at any time.

The input pulse width is calculated by subtracting the value in B1 from A2.

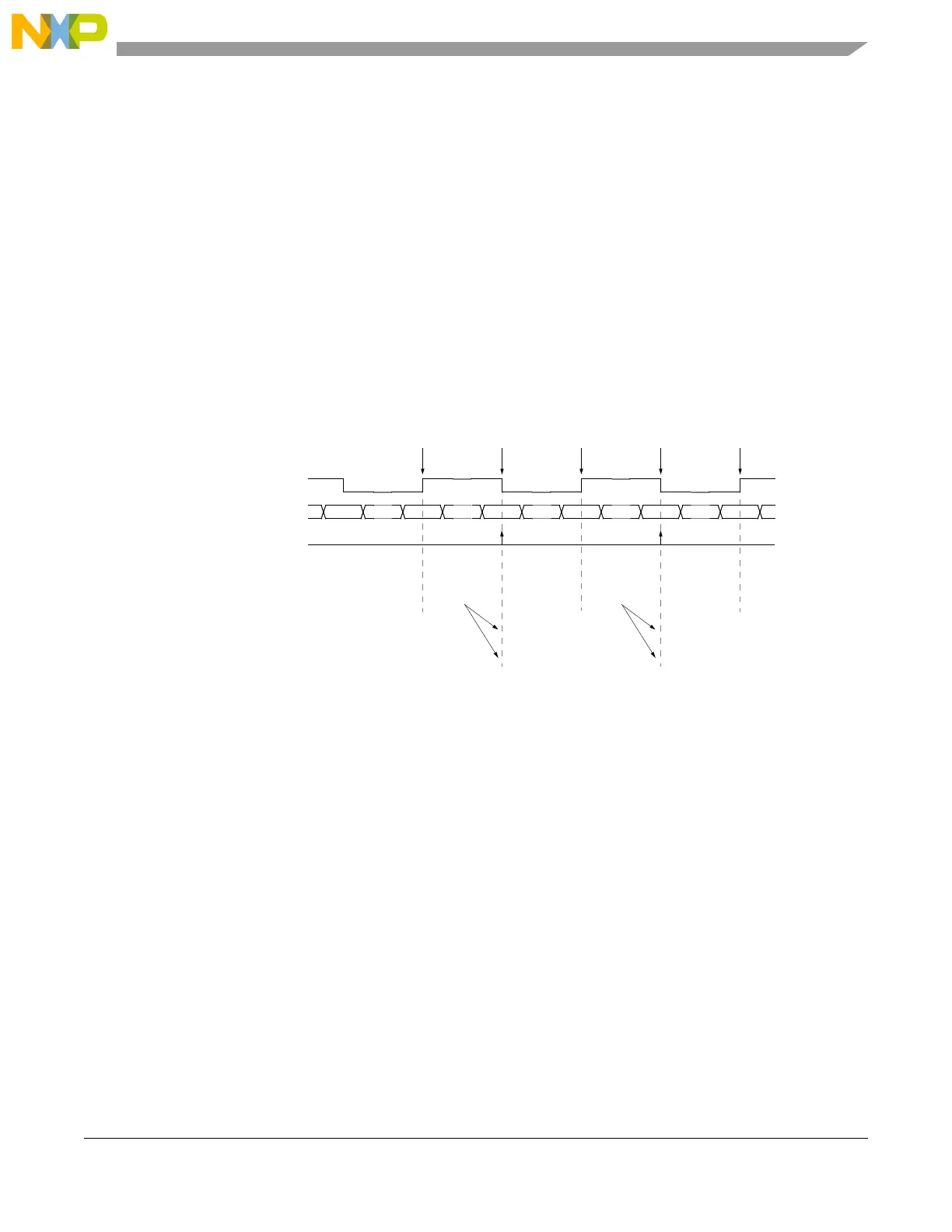

Figure 24-23 shows how the Unified Channel can be used for input pulse width measurement.

Figure 24-23. Input pulse width measurement example

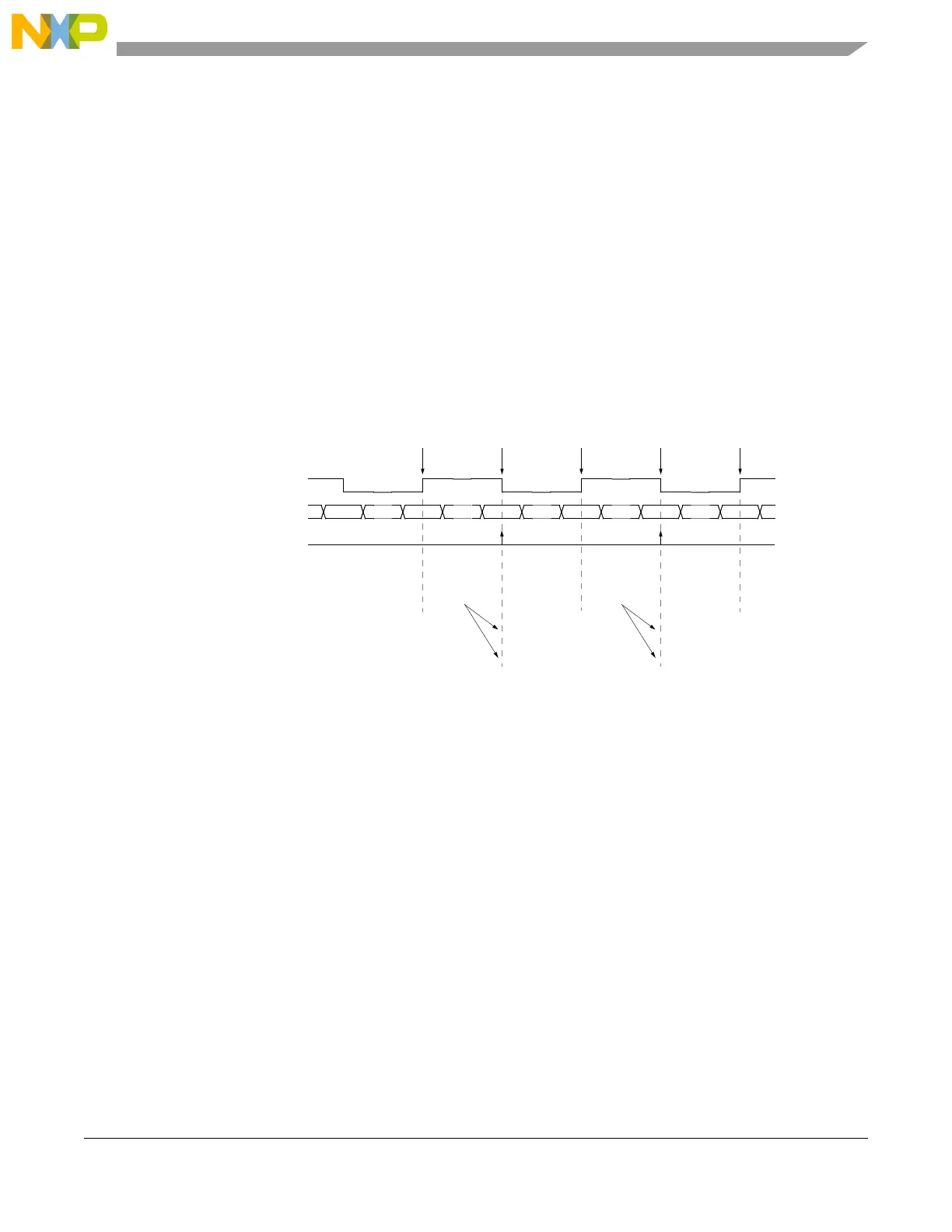

Figure 24-24 shows the A1 and B1 updates when EMIOSA[n] and EMIOSB[n] register reads occur. Note

that A1 register has always coherent data related to A2 register. Note also that when EMIOSA[n] read is

performed B1 register is loaded with A1 register content. This guarantee that the data in register B1 has

always the coherent data related to the last EMIOSA[n] read. The B1 register updates remains locked until

EMIOSB[n] read occurs. If EMIOSA[n] read is performed B1 is updated with A1 register content even if

B1 update is locked by a previous EMIOSA[n] read operation.

selected counter bus 0x000500 0x001000 0x001100 0x001250 0x001525 0x0016A0

A2(captured) value

2

B2(captured) value

B1 value

3

0xxxxxxx 0x001000 0x001250 0x0016A0

0xxxxxxx 0x001100 0x001525

0xxxxxxx 0x001000 0x001250

Input signal

1

BABAB

1. After input filter

Notes:

FLAG pin/register

2. EMIOSA[n] = A2

3. EMIOSB[n] = B1

EDPOL = 1

A1 value

3

0xxxxxxx 0x001000 0x001250

Loading...

Loading...