MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 583

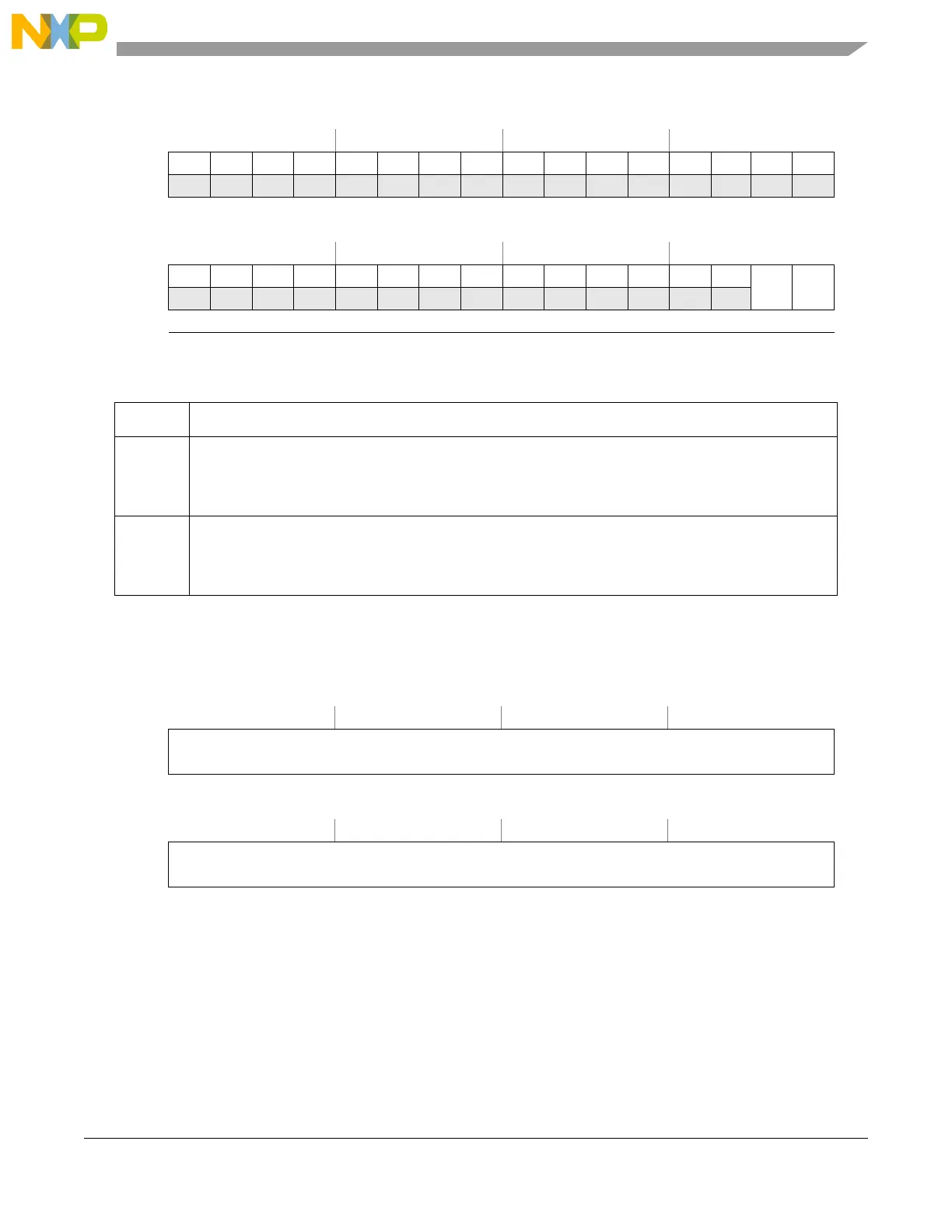

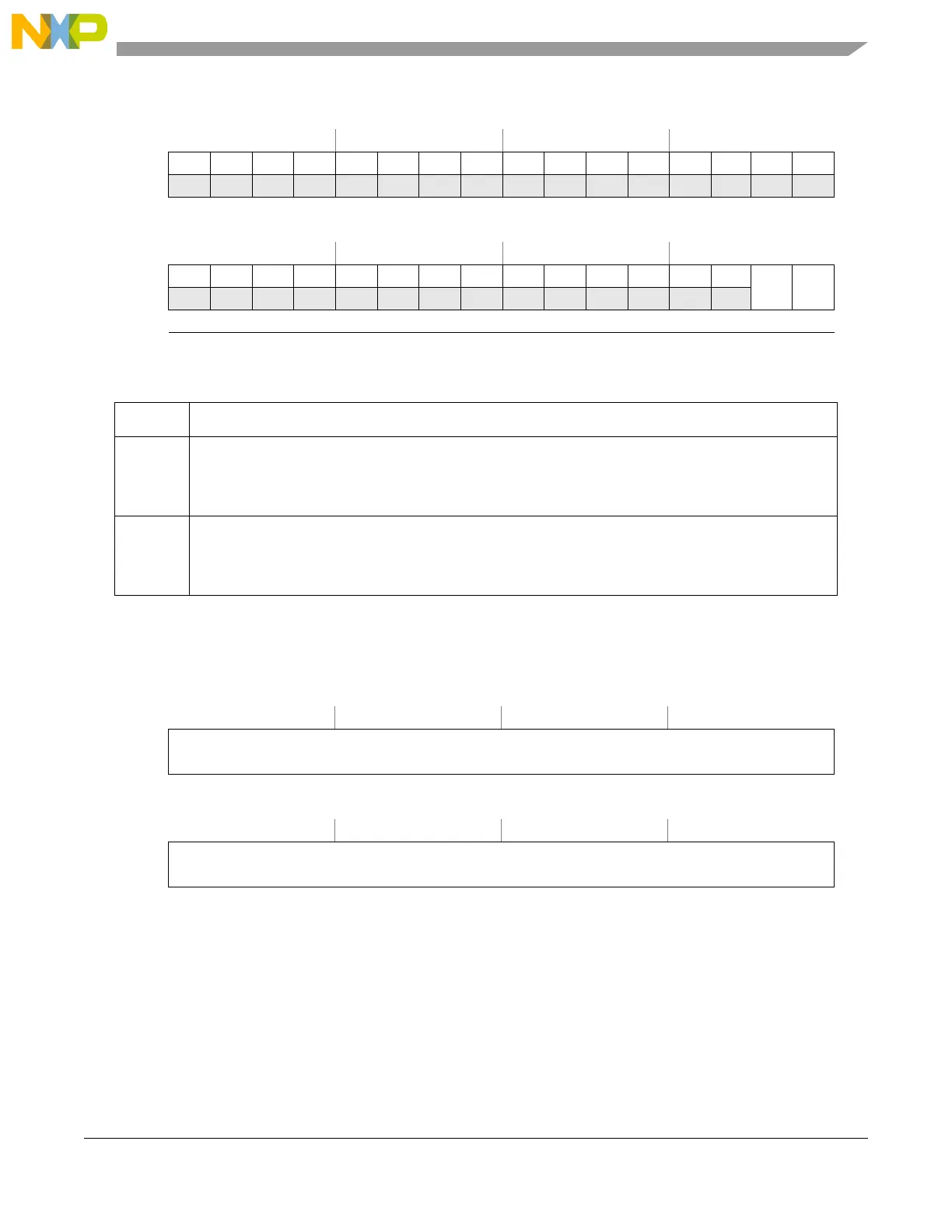

24.5.4.3 Timer Load Value Register (LDVAL)

This register selects the timeout period for the timer interrupts.

Offset: 0x000 Access: Read/Write

0123456789101112131415

R 0 0 0 0 0 00000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 0 0 0 0 00000 000 0

MDIS FRZ

W

Reset0000000000000010

Figure 24-57. PIT Module Control Register (PITMCR)

Table 24-25. PITMCR field descriptions

Field Description

MDIS Module Disable

This is used to disable the module clock. This bit should be enabled before any other setup is done.

0 Clock for PIT timers is enabled

1 Clock for PIT timers is disabled (default)

FRZ Freeze

Allows the timers to be stopped when the device enters debug mode.

0 = Timers continue to run in debug mode.

1 = Timers are stopped in debug mode.

Offset: channel_base + 0x00 Access: Read/Write

0123456789101112131415

R

TSV[31:16]

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

TSV[15:0]

W

Reset0000000000000000

Figure 24-58. Timer Load Value Register (LDVAL)

Loading...

Loading...