MPC5604B/C Microcontroller Reference Manual, Rev. 8

582 Freescale Semiconductor

NOTE

Register Address = Base Address + Address Offset, where the Base Address

is defined at the MCU level and the Address Offset is defined at the module

level.

NOTE

Reserved registers will read as 0, writes will have no effect.

24.5.4.2 PIT Module Control Register (PITMCR)

This register controls whether the timer clocks should be enabled and whether the timers should run in

debug mode.

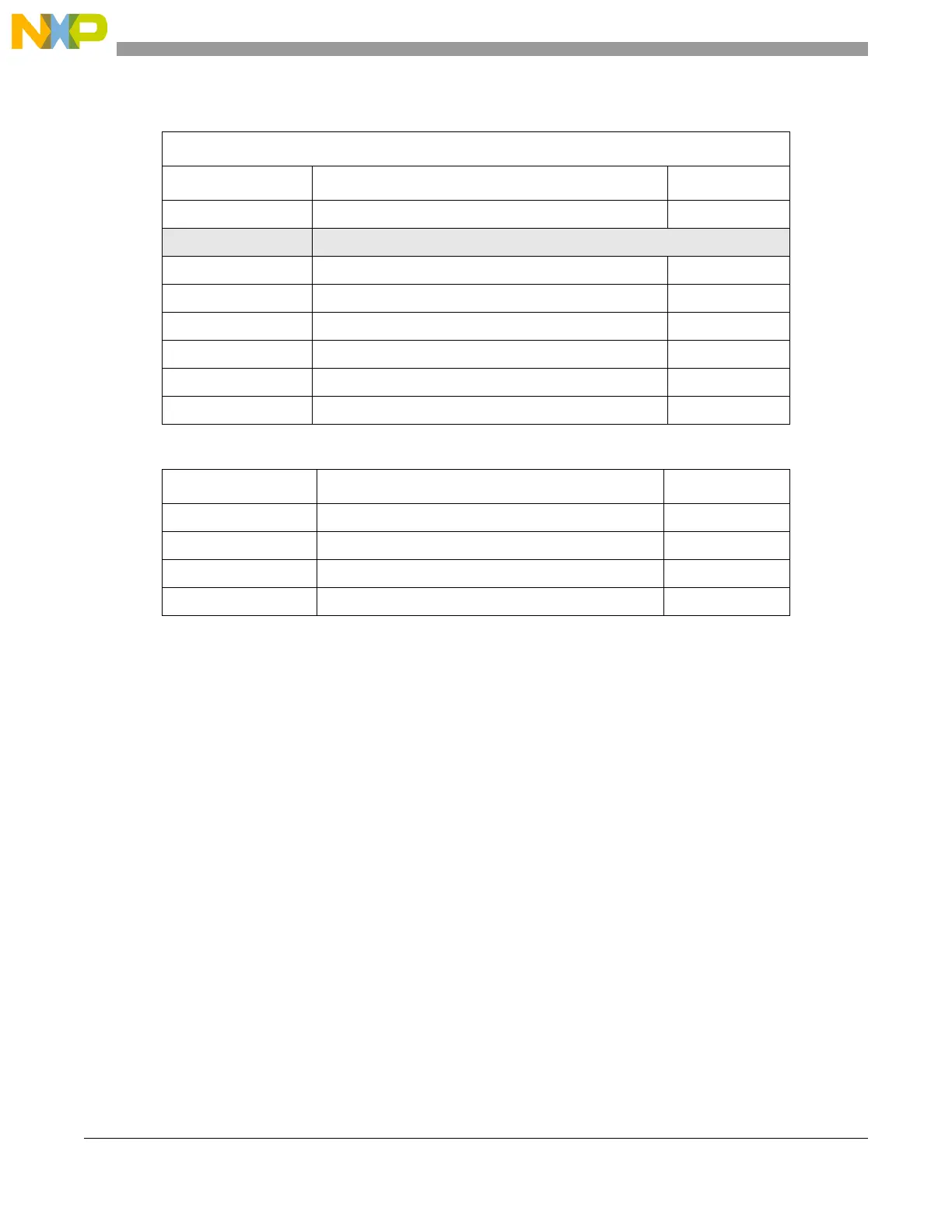

Table 24-23. PIT memory map

Base address: 0xC3FF_0000

Address offset Use Location

0x000 PIT Module Control Register (PITMCR) on page 582

0x004–0x0FC Reserved

0x100–0x10C Timer Channel 0 See Table 24-24

0x110–0x11C Timer Channel 1 See Table 24-24

0x120–0x12C Timer Channel 2 See Table 24-24

0x130–0x13C Timer Channel 3 See Table 24-24

0x140–0x14C Timer Channel 4 See Table 24-24

0x150–0x15C Timer Channel 5 See Table 24-24

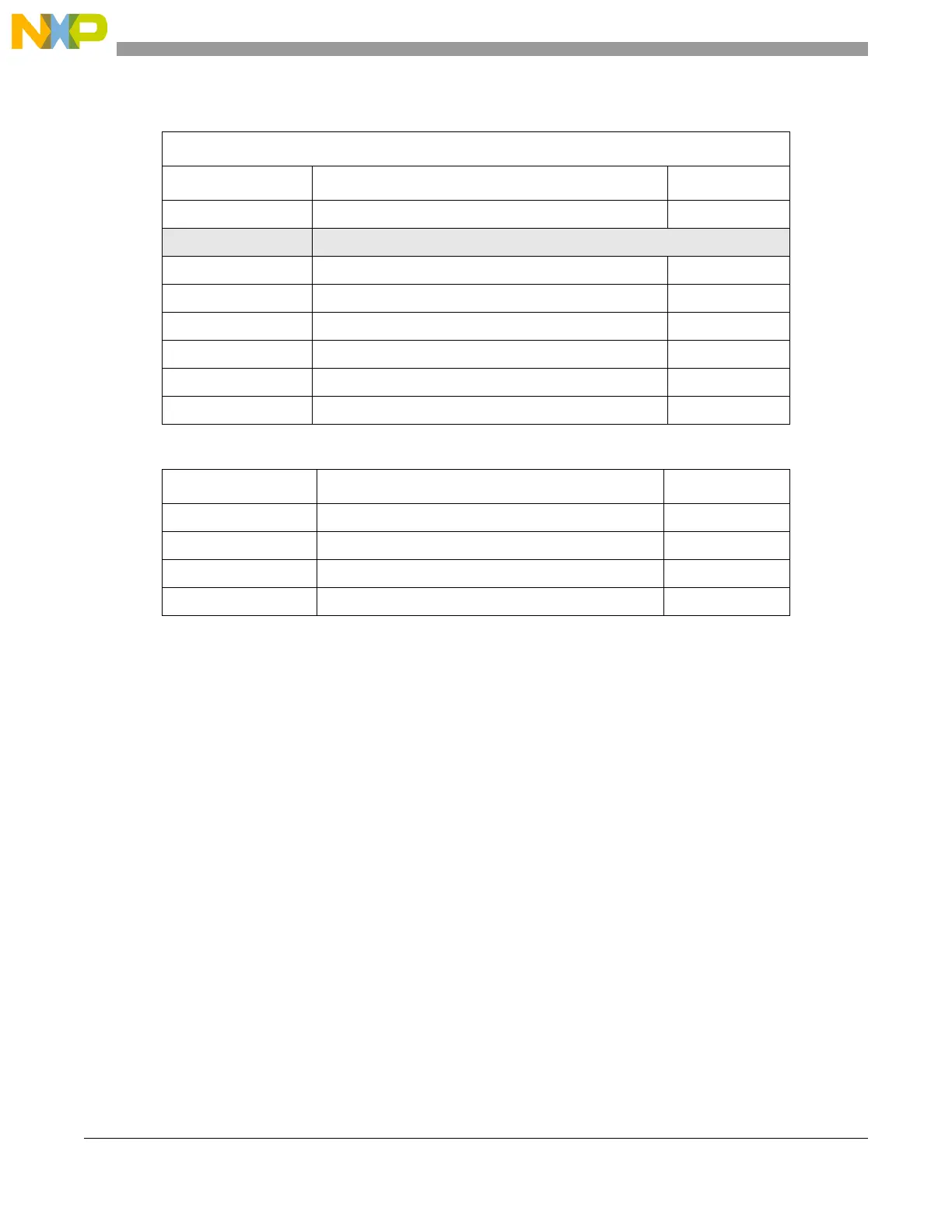

Table 24-24. Timer channel n

Address offset Use Location

channel + 0x00 Timer Load Value Register (LDVAL) on page 583

channel + 0x04 Current Timer Value Register (CVAL) on page 584

channel + 0x08 Timer Control Register (TCTRL) on page 584

channel + 0x0C Timer Flag Register (TFLG) on page 585

Loading...

Loading...