MPC5604B/C Microcontroller Reference Manual, Rev. 8

614 Freescale Semiconductor

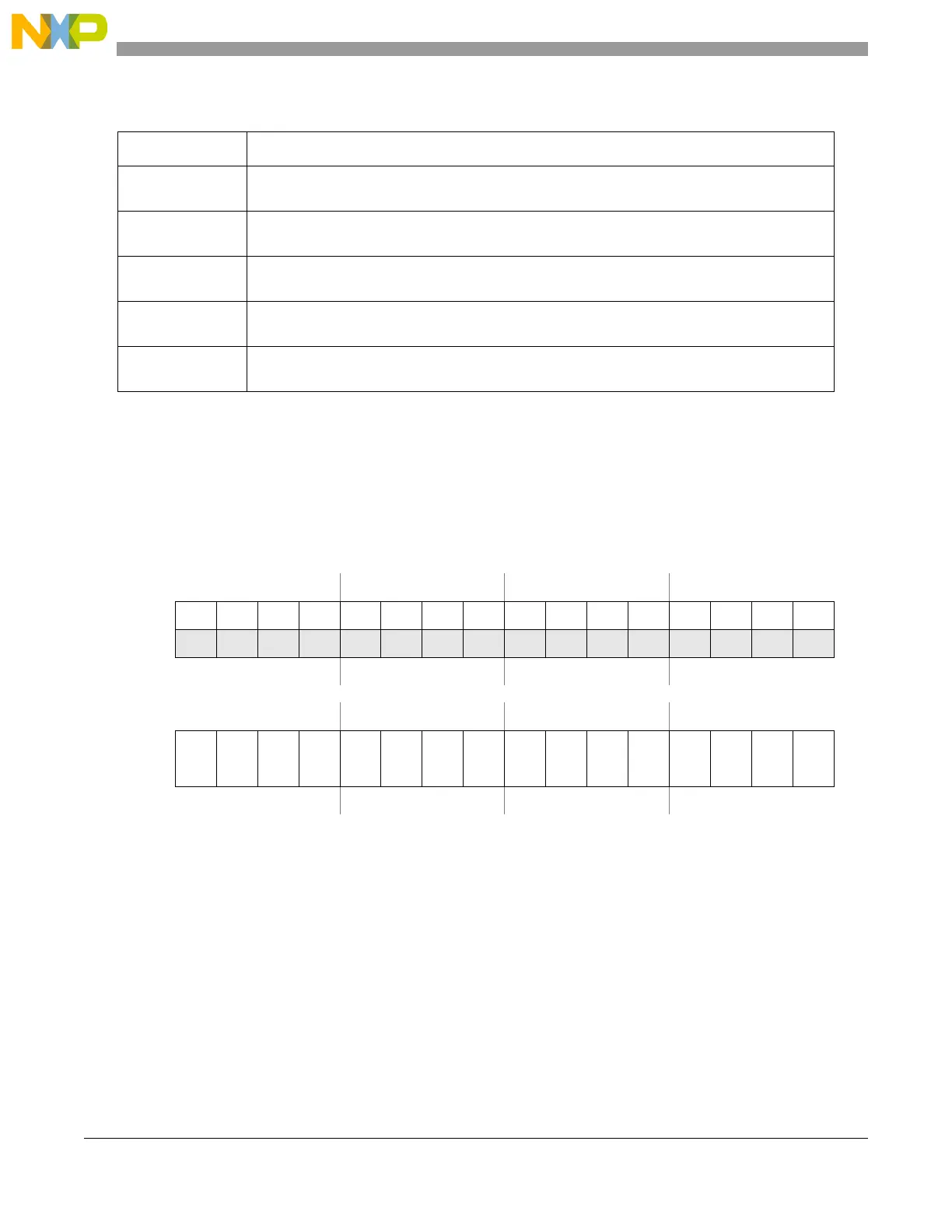

25.4.3.4 Channel Interrupt Mask Register (CIMR[0..2])

CIMR0 = Enable bits for channel 0 to 15 (precision channels)

CIMR1 = Enable bits for channel 32 to 47 (standard channels)

CIMR2 = Enable bits for channel 64 to 95 (external multiplexed channels)

Table 25-11. Interrupt Mask Register (IMR) field descriptions

Field Description

MSKEOCTU Mask for end of CTU conversion (EOCTU) interrupt

When set, the EOCTU interrupt is enabled.

MSKJEOC Mask for end of injected channel conversion (JEOC) interrupt

When set, the JEOC interrupt is enabled.

MSKJECH Mask for end of injected chain conversion (JECH) interrupt

When set, the JECH interrupt is enabled.

MSKEOC Mask for end of channel conversion (EOC) interrupt

When set, the EOC interrupt is enabled.

MSKECH Mask for end of chain conversion (ECH) interrupt

When set, the ECH interrupt is enabled.

Address:

Base + 0x0024 Access: User read/write

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

CIM

15

CIM

14

CIM

13

CIM

12

CIM

11

CIM

10

CIM

9

CIM

8

CIM

7

CIM

6

CIM

5

CIM

4

CIM

3

CIM

2

CIM

1

CIM

0

W

Reset0000000000000000

Figure 25-15. Channel Interrupt Mask Register 0 (CIMR0)

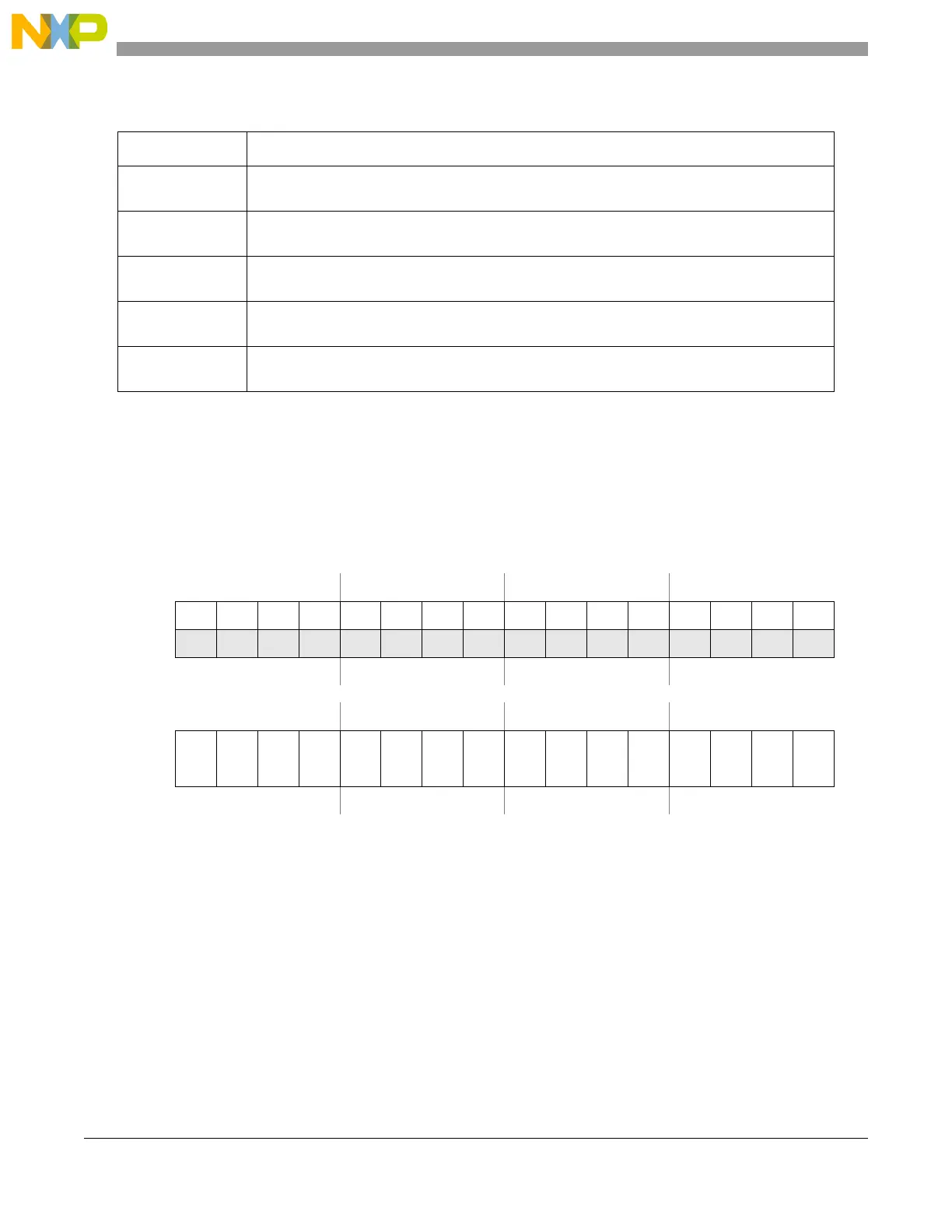

Loading...

Loading...