MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 665

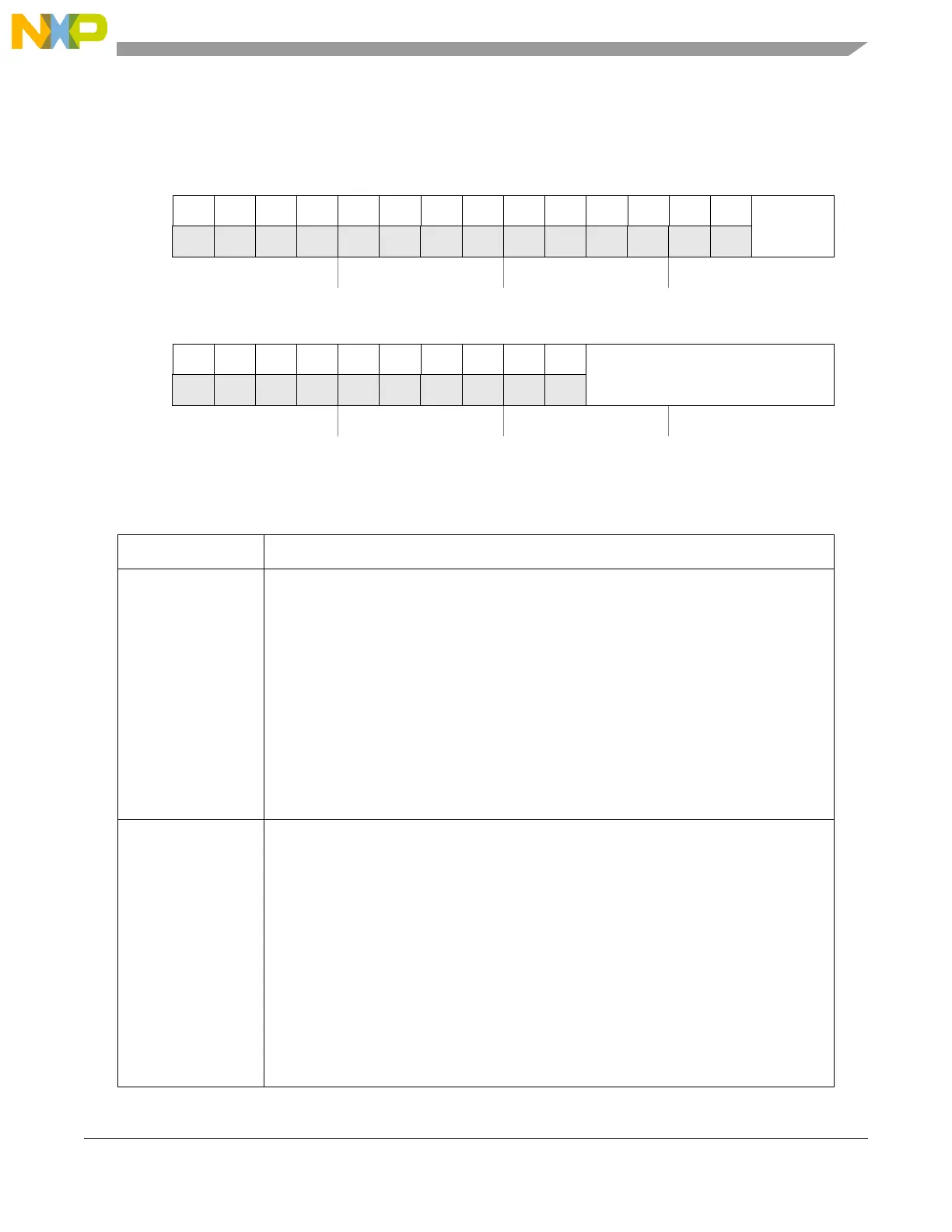

27.5.1.4 CFlash Low/Mid Address Space Block Select Register (CFLASH_LMS)

The CFLASH_LMS register provides a means to select blocks to be operated on during erase.

Offset: 0x00010 Access: Read/write

0123456789101112131415

R

00000000000000

MSL

W

Reset

0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0000000000

LSL

W

Reset

0000000000000000

Figure 27-8. CFlash Low/Mid address space block Select register (CFLASH_LMS)

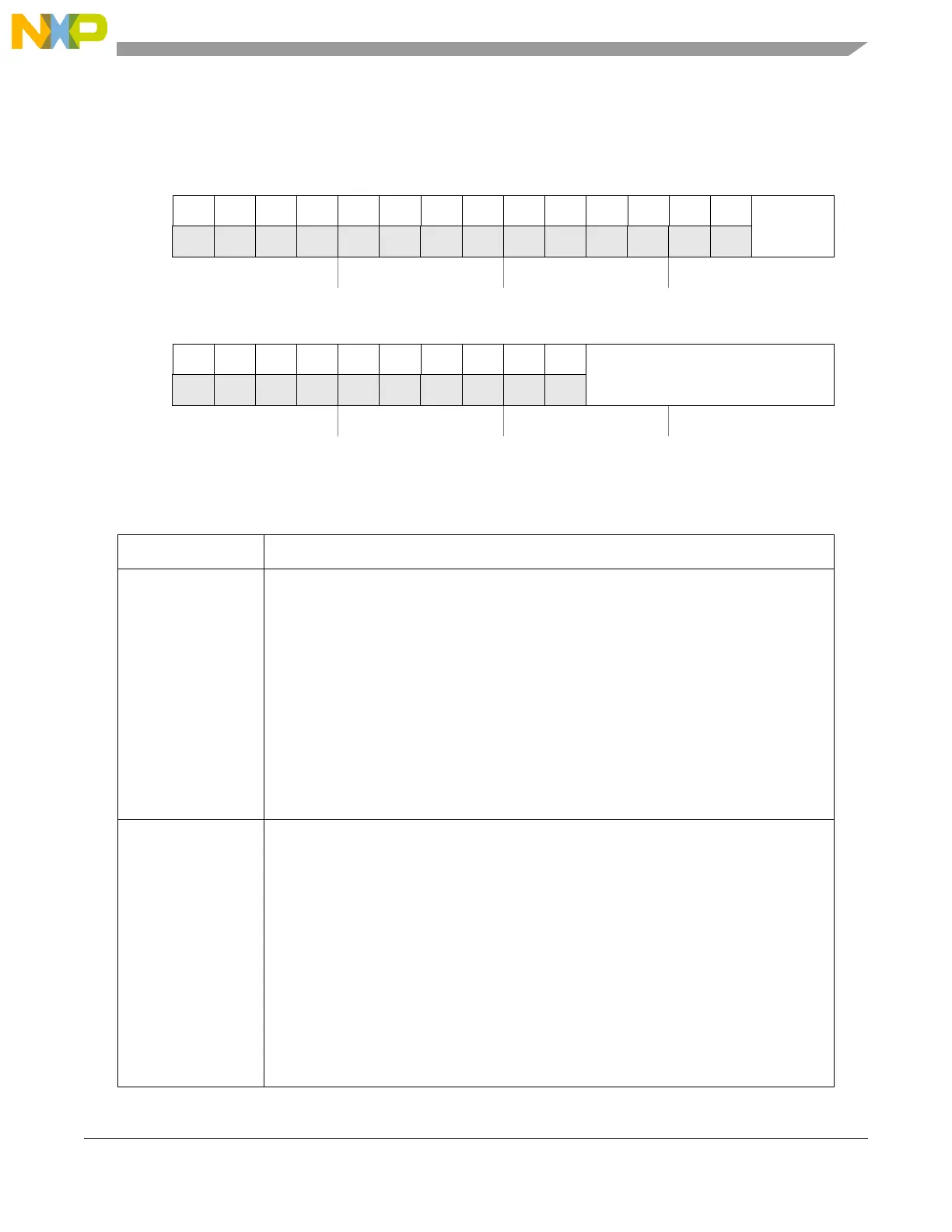

Table 27-18. CFLASH_LMS field descriptions

Field Description

MSL Mid address space block SeLect

A value of 1 in the select register signifies that the block is selected for erase.

A value of 0 in the select register signifies that the block is not selected for erase. The reset

value for the select register is 0, or unselected.

MSL[1:0] are related to sectors B0F7-6, respectively.

The blocks must be selected (or unselected) before doing an erase interlock write as part of

the erase sequence. The select register is not writable once an interlock write is completed

or if a high voltage operation is suspended.

In the event that blocks are not present (due to configuration or total memory size), the

corresponding MSL bits will default to unselected, and will not be writable. The reset value

will always be 0, and register writes will have no effect.

0: Mid Address Space Block is unselected for erase.

1: Mid Address Space Block is selected for erase.

LSL Low address space block SeLect

A value of 1 in the select register signifies that the block is selected for erase.

A value of 0 in the select register signifies that the block is not selected for erase. The reset

value for the select register is 0, or unselected.

LSL[5:0] are related to sectors B0F5-0, respectively. LSL[15:6] are not used for this memory

cut.

The blocks must be selected (or unselected) before doing an erase interlock write as part of

the erase sequence. The select register is not writable once an interlock write is completed

or if a high voltage operation is suspended.

In the event that blocks are not present (due to configuration or total memory size), the

corresponding LSL bits will default to unselected, and will not be writable. The reset value

will always be 0, and register writes will have no effect.

Bits LSL[15:6] are read-only and locked at ‘0’.

0: Low Address Space Block is unselected for erase.

1: Low Address Space Block is selected for erase.

Loading...

Loading...