MPC5604B/C Microcontroller Reference Manual, Rev. 8

808 Freescale Semiconductor

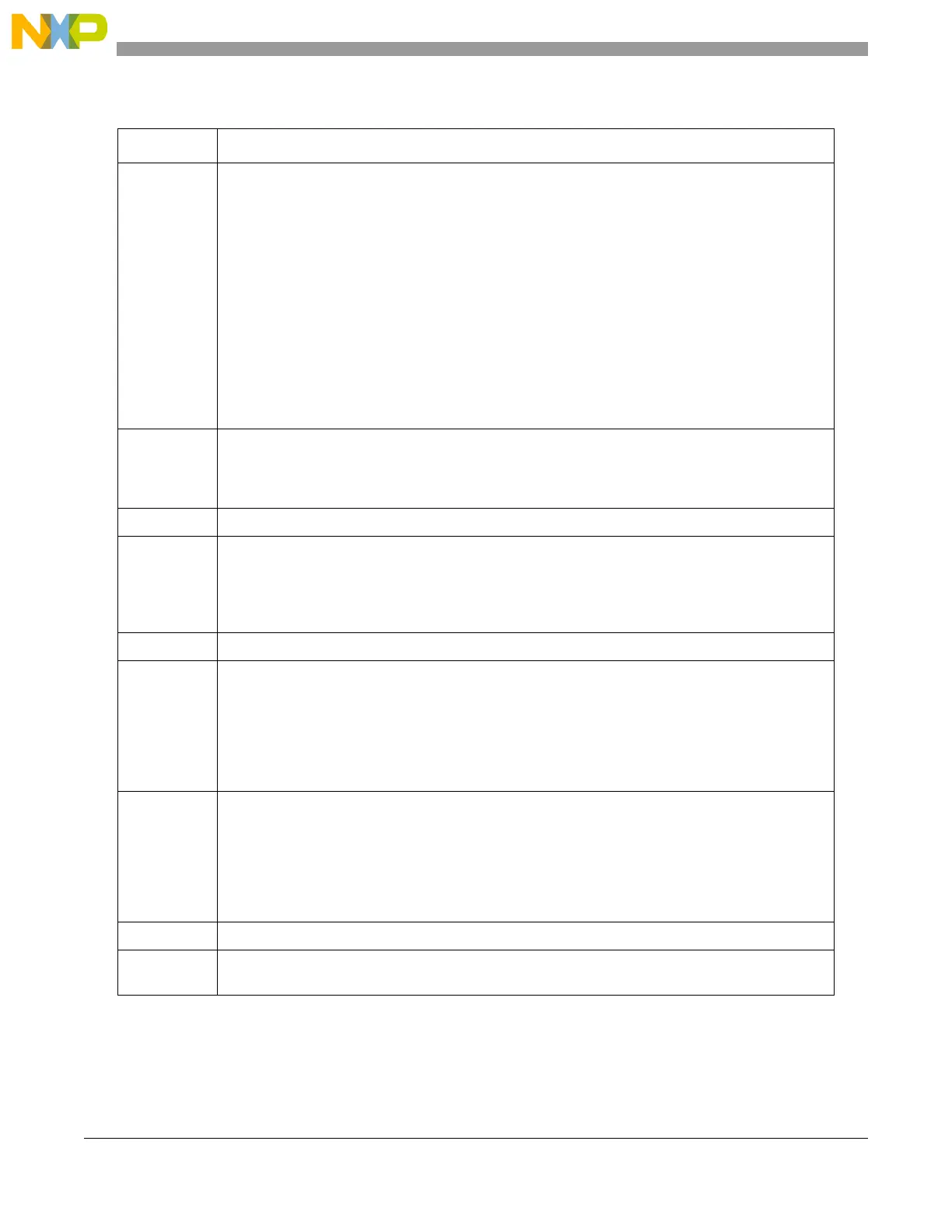

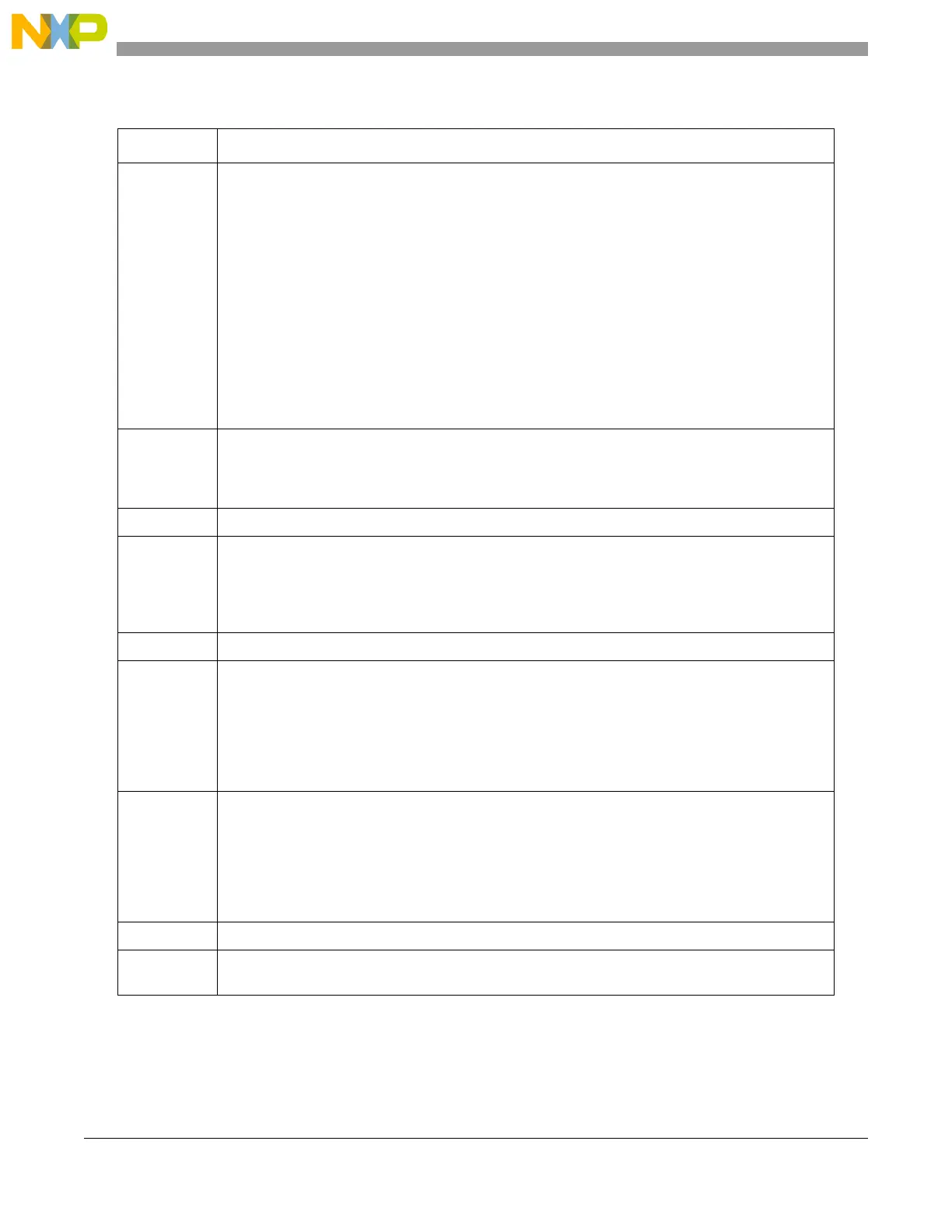

3–5

MCKO_DIV

[2:0]

MCKO Division Factor

The value of this signal determines the frequency of MCKO relative to the system clock frequency

when MCKO_EN is asserted. SYS_CLK represents the system clock frequency:

Note: MCKO_DIV value and associated MCKO frequency should be configured taking into account

the frequency limitation of the associated MCKO pad. Please refer to datasheet IO section.

6

EVT_EN

EVTO/EVTI Enable

This bit enables the EVTO/EVTI port functions.

0 EVTO/EVTI port disabled

1 EVTO/EVTI port enabled

7–15 Reserved

16

LP_DBG_EN

Low Power Debug Enable

The LP_DBG_EN bit enables debug functionality to support entry and exit from low power sleep and

STOP modes.

0 Low power debug disabled

1 Low power debug enabled

17–21 Reserved

22

SLEEP_SYN

C

Sleep Mode Synchronization

The SLEEP_SYNC bit is used to synchronize the entry into sleep mode between the device and

debug tool. The device sets this bit before a pending entry into sleep mode. After reading

SLEEP_SYNC as set, the debug tool then clears SLEEP_SYNC to acknowledge to the device that

it may enter into sleep mode.

0 Sleep mode entry acknowledge

1 Sleep mode entry pending

23

STOP_SYNC

Stop Mode Synchronization

The STOP_SYNC bit is used to synchronize the entry into STOP mode between the device and

debug tool. The device sets this bit before a pending entry into STOP mode. After reading

STOP_SYNC as set, the debug tool then clears STOP_SYNC to acknowledge to the device that it

may enter into STOP mode.

0 Stop mode entry acknowledge

1 Stop mode entry pending

24–30 Reserved

31

PSTAT_EN

Processor Status Mode Enable

Table 33-4. PCR field descriptions (continued)

Field Description

Value MCKO frequency

0b000 SYS_CLK

0b001 SYS_CLK2 (default value if a reserved encoding is

programmed)

0b010 Reserved

0b011 SYS_CLK4

0b100 Reserved

0b101 Reserved

0b110 Reserved

0b111 SYS_CLK8

Loading...

Loading...