MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 809

33.6.2.3 Development Control Register 1, 2 (DC1, DC2)

The development control registers are used to control the basic development features of the Nexus module.

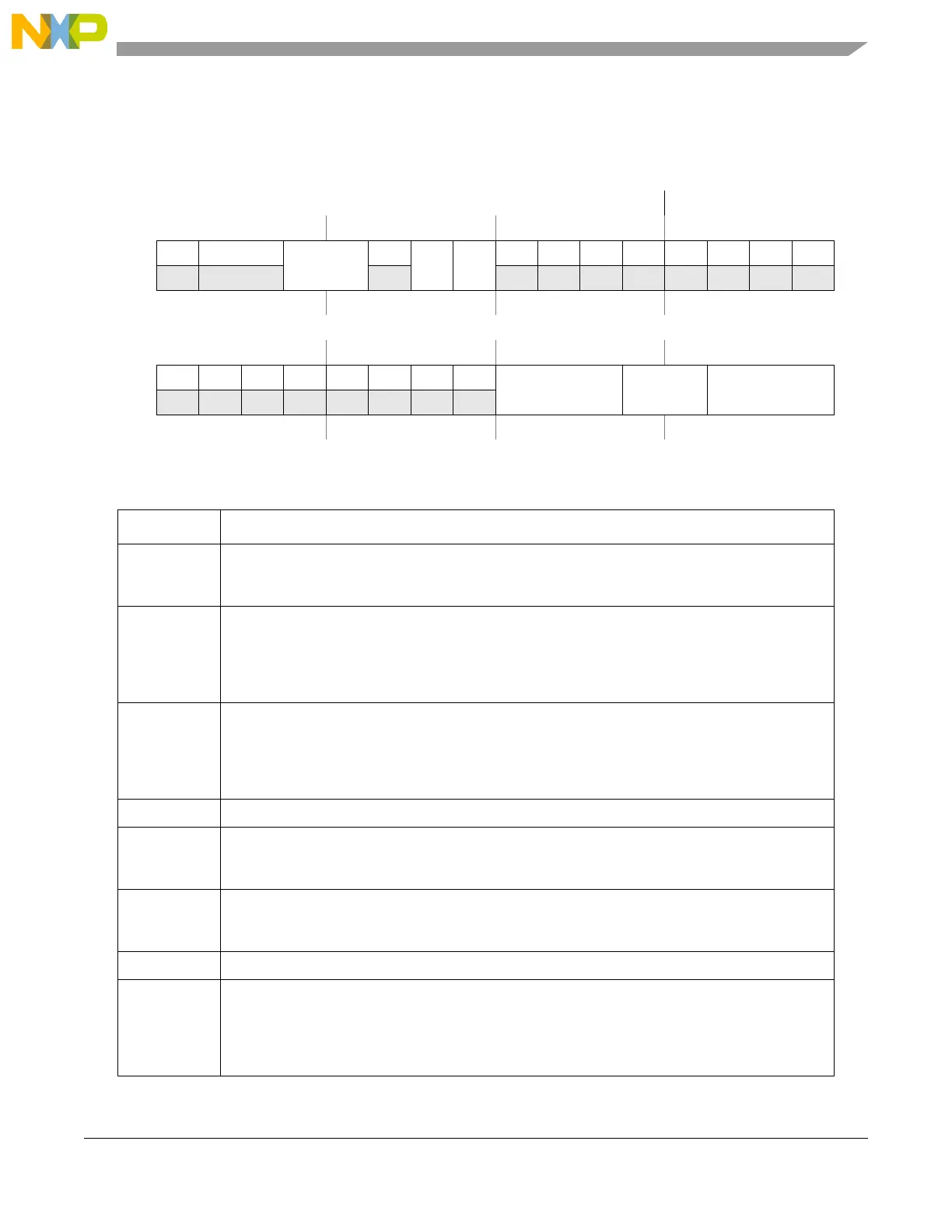

Figure 33-5 shows development control register 1 and Table 33-5 describes the register’s fields.

Nexus Reg: 0x0002 Access: User read/write

0123456789101112131415

ROPCMCK_DIV EOC 0PTMWEN00000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

OVC EIC TM

W

Reset0000000000000000

Figure 33-5. Development Control Register 1 (DC1)

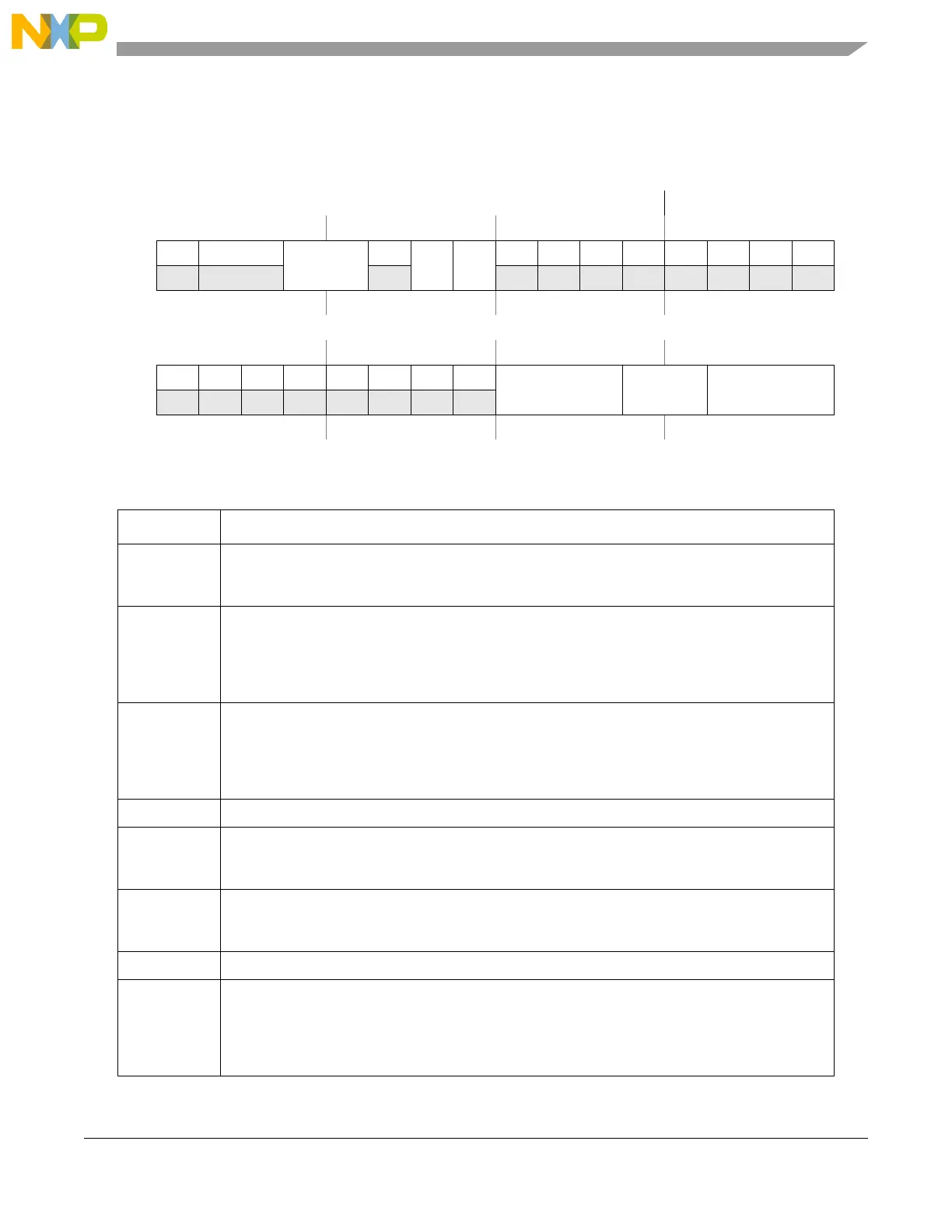

Table 33-5. DC1 field descriptions

Field Description

0

OPC

1

Output Port Mode Control

0 Reduced-port mode configuration (2 MDO pins)

1 Full-port mode configuration (4 MDO pins)

1–2

MCK_DIV[1:0]

1

MCKO Clock Divide Ratio (see note below)

00 MCKO is 1x processor clock freq.

01 MCKO is 1/2x processor clock freq.

10 MCKO is 1/4x processor clock freq.

11 MCKO is 1/8x processor clock freq.

3–4

EOC[1:0]

EVTO Control

00 EVTO upon occurrence of watchpoints (configured in DC2)

01 EVTO upon entry into debug mode

10 EVTO upon timestamping event

11 Reserved

5Reserved

6

PTM

Program Trace Method

0 Program trace uses traditional branch messages.

1 Program trace uses branch history messages.

7

WEN

Watchpoint Trace Enable

0 Watchpoint messaging disabled

1 Watchpoint messaging enabled

8–23 Reserved

24–26

OVC[2:0]

Overrun Control

000 Generate overrun messages.

001–010 Reserved

011 Delay processor for BTM / DTM / OTM overruns.

1XX Reserved

Loading...

Loading...