Using Performance Monitoring Events B

B-29

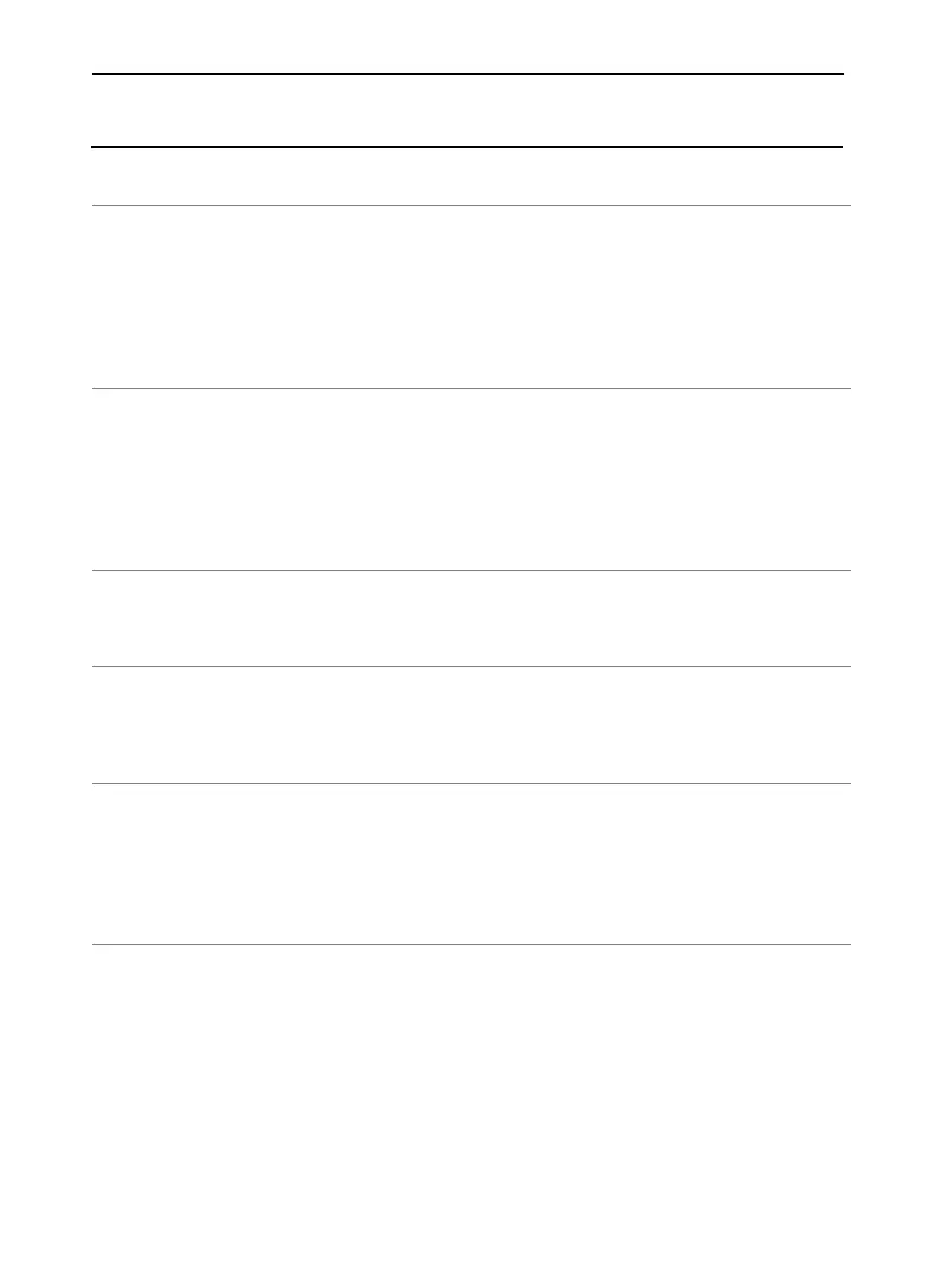

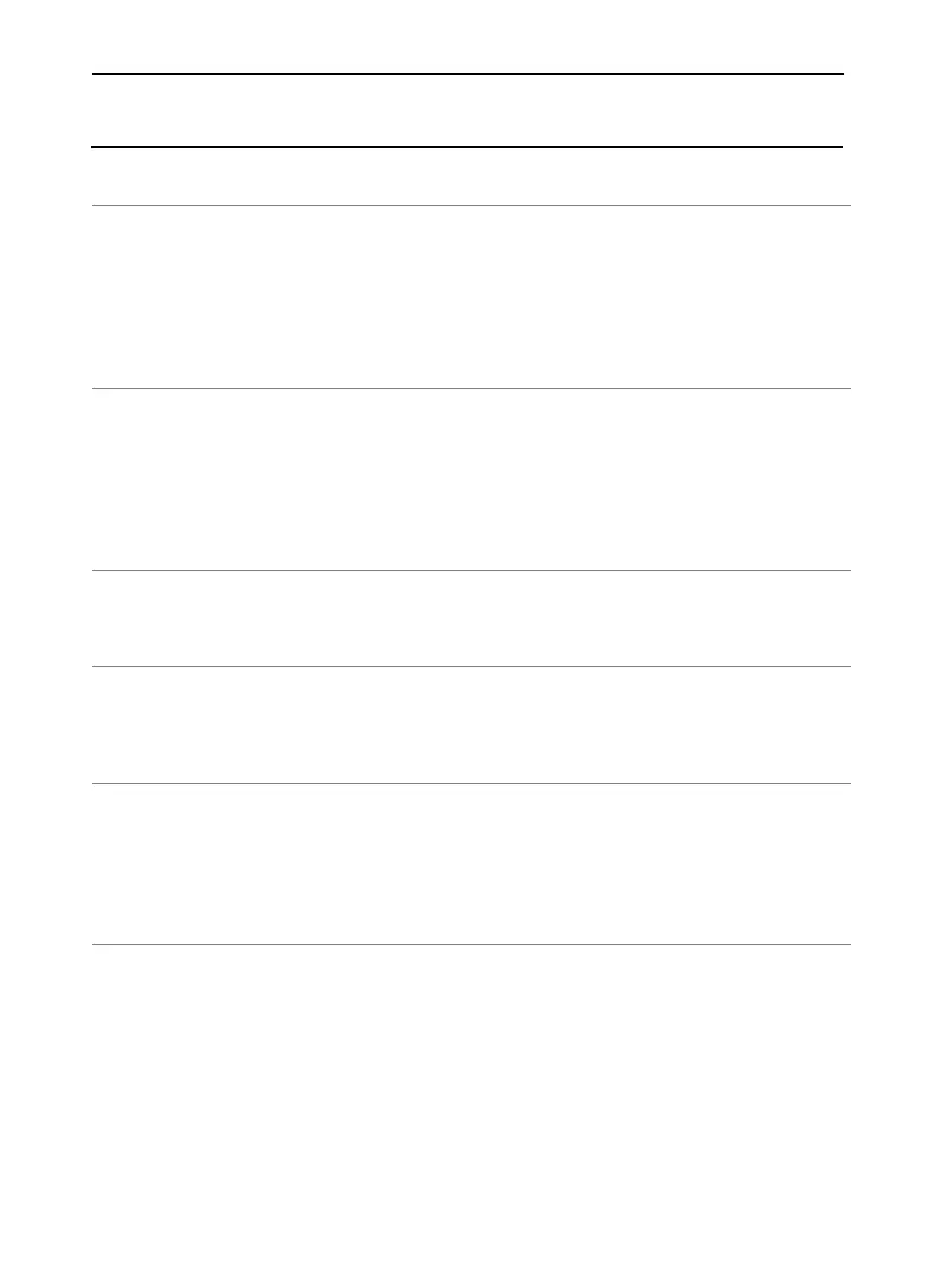

3rd-Level

Cache Reads

Hit Modified

The number of

3rd-level cache read

references (loads

and RFOs) that hit

the cache line in

modified state.

Beware of granularity

differences.

BSQ_cache_reference RD_3rdL_HITM

3rd-Level

Cache Reads

Hit Exclusive

The number of

3rd-level cache read

references (loads

and RFOs) that hit

the cache line in

exclusive state.

Beware of granularity

differences.

BSQ_cache_reference RD_3rdL_HITE

MOB Load

Replays Retired

The number of

retired load μops that

experienced replays

related to the MOB.

Replay_event; set the

following replay tag:

MOB_load_replay_

retired

NBOGUS

Loads Retired The number of

retired load

operations that were

tagged at the front

end.

Front_end_event; set

the following front end

tag: Memory_loads

NBOGUS

Stores Retired The number of

retired stored

operations that were

tagged at the front

end. This stat is often

used in a

per-instruction ratio.

Front_end_event; set

the following front end

tag: Memory_stores

NBOGUS

continued

Table B-1 Pentium 4 Processor Performance Metrics (continued)

Metric Description

Event Name or Metric

Expression

Event Mask Value

Required

Loading...

Loading...