MPC5604B/C Microcontroller Reference Manual, Rev. 8

654 Freescale Semiconductor

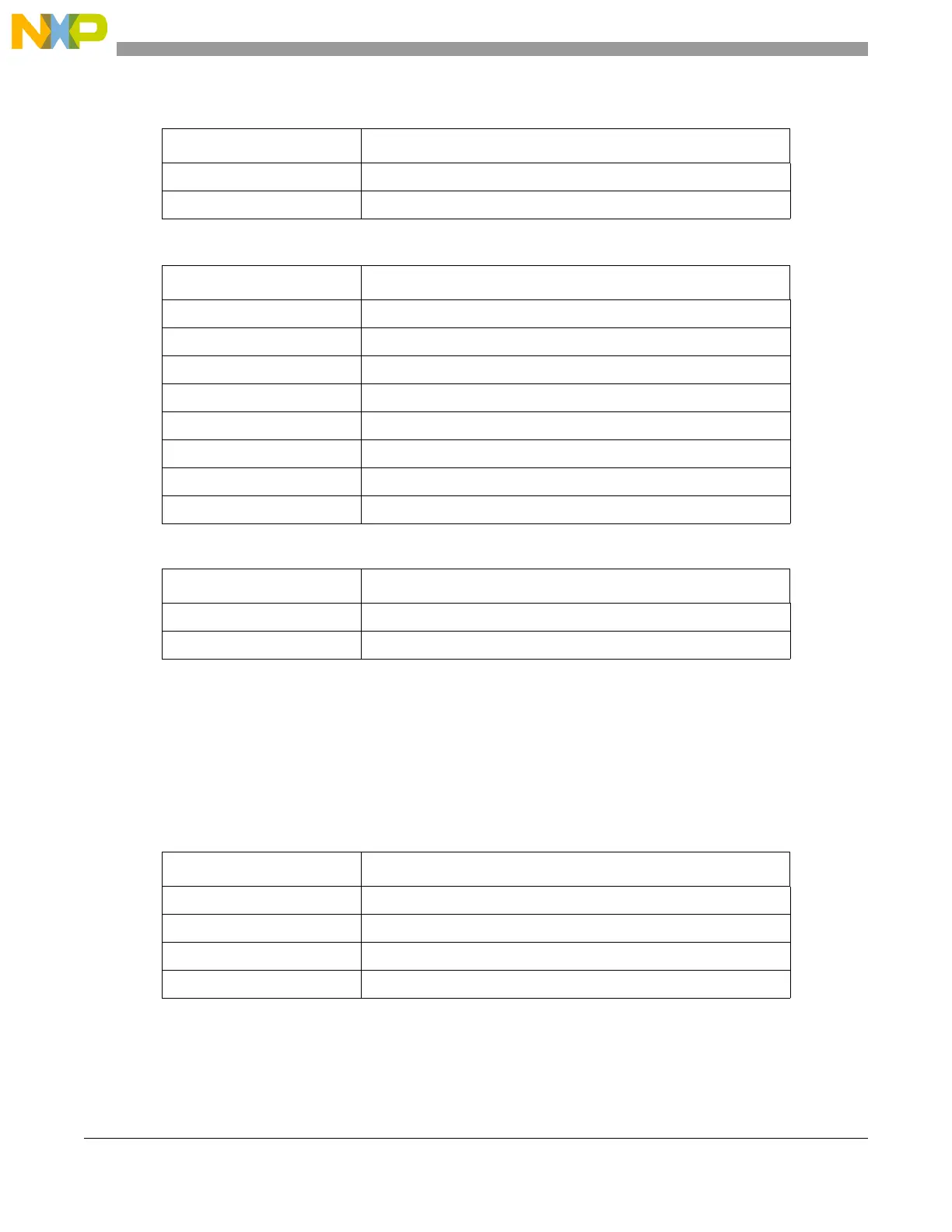

A number of CFLASH_MCR bits are protected against write when another bit, or set of bits, is in a specific

state. These write locks are covered on a bit by bit basis in the preceding description, but those locks do

not consider the effects of trying to write two or more bits simultaneously.

The flash memory module does not allow the user to write bits simultaneously which would put the device

into an illegal state. This is implemented through a priority mechanism among the bits. The bit changing

priorities are detailed in Table 27-13.

If the user attempts to write two or more CFLASH_MCR bits simultaneously then only the bit with the

lowest priority level is written.

110 64 KB

111 Reserved

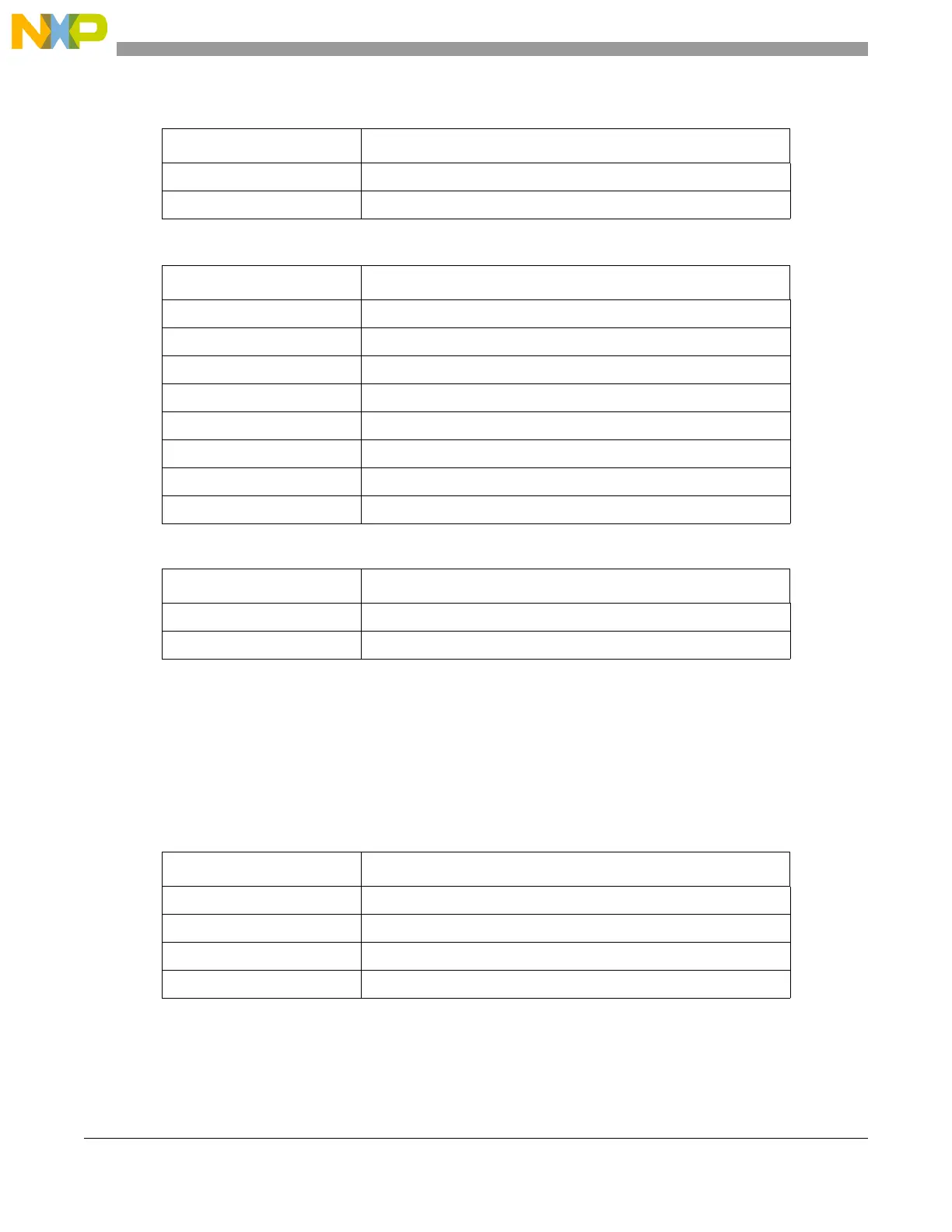

Table 27-11. Low address space configuration

LAS Low address space sectorization

000 Reserved

001 Reserved

010 32 KB + 2 x 16 KB + 2 x 32 KB + 128 KB

011 Reserved

100 Reserved

101 Reserved

110 4 x 16 KB

111 Reserved

Table 27-12. Mid address space configuration

MAS Mid address space sectorization

0 2 x 128 KB or 0 KB

1 Reserved

Table 27-13. CFLASH_MCR bits set/clear priority levels

Priority level CFLASH_MCR bits

1ERS

2PGM

3EHV

4 ESUS

Table 27-10. Array space size (continued)

SIZE Array space size

Loading...

Loading...