MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 719

See the MPC5604B data sheet for detailed settings for different values of frequency.

27.7.2.2 Register description

This section details the individual registers of the platform flash memory controller.

Flash memory configuration registers must be written only with 32-bit write operations to avoid any issues

associated with register “incoherency” caused by bits spanning smaller-size (8- or 16-bit) boundaries.

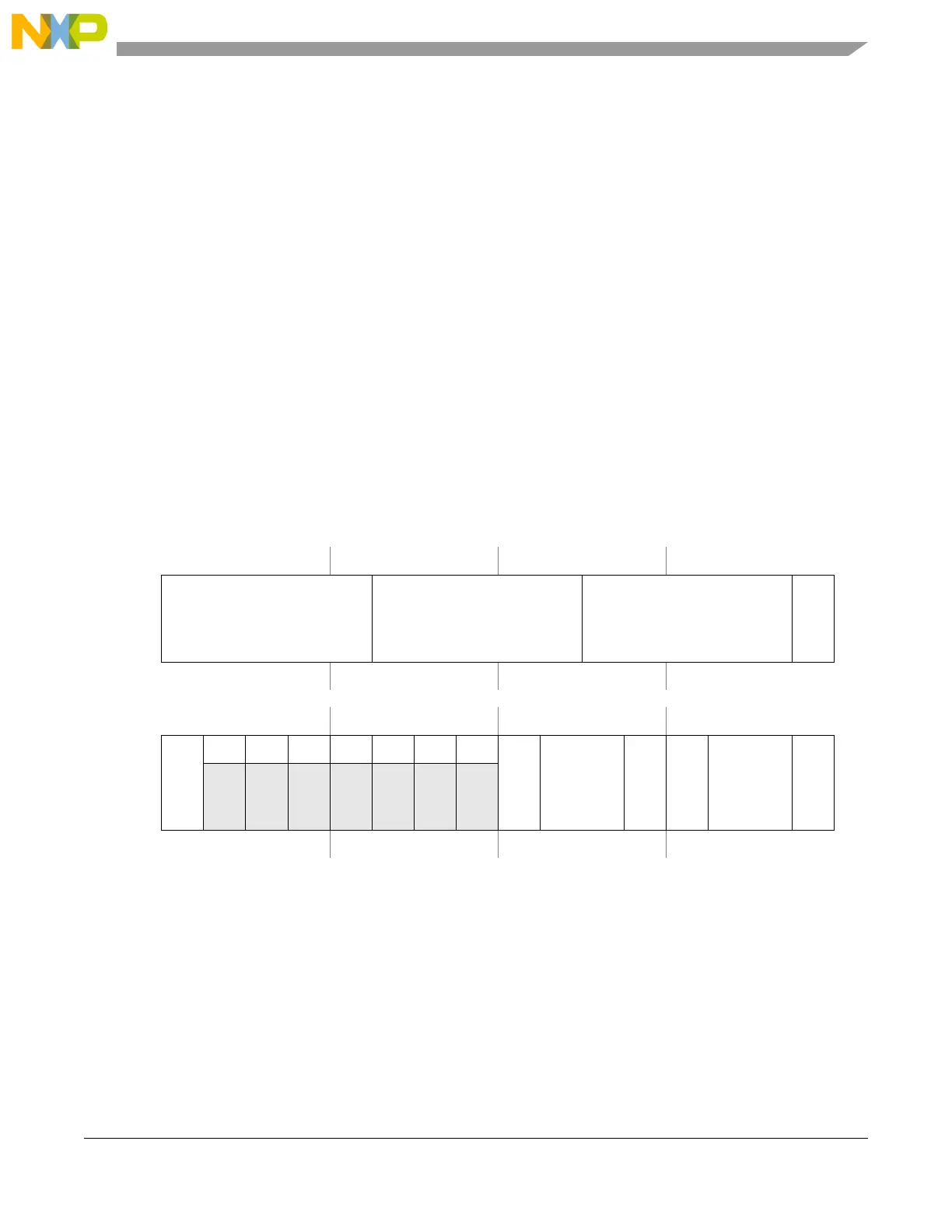

27.7.2.2.1 Platform Flash Configuration Register 0 (PFCR0)

This register defines the configuration associated with the code flash memory bank0. It includes fields that

provide specific information for up to two separate AHB ports (p0 and the optional p1). For the platform

flash memory controller module, the fields associated with AHB port p1 are ignored. The register is

described in Figure 27-39 and Table 27-58.

NOTE

Do not execute code from flash memory when you are programming

PFCR0. If you wish to program PFCR0, execute your application code from

RAM.

Offset 0x01C Access: Read/write

0123456789101112131415

R

BK0_APC BK0_WWSC BK0_RWSC

BK0_RWWC

W

Reset0001100011000111

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

BK0_RWWC

0000000

BK0_RWWC

B0_P0_BCFG

B0_P0_DPFE

B0_P0_IPFE

B0_P0_PFLM

B0_P0_BFE

W

Reset1000000011101101

Figure 27-39. PFlash Configuration Register 0 (PFCR0)

Loading...

Loading...