RM0402 Rev 6 1099/1163

RM0402 USB on-the-go full-speed (OTG_FS)

1122

1. Program the OTG_DOEPTSIZx register.

– STUPCNT = 3

2. Wait for the RXFLVL interrupt (OTG_GINTSTS) and empty the data packets from the

receive FIFO.

3. Assertion of the STUP interrupt (OTG_DOEPINTx) marks a successful completion of

the SETUP data transfer.

– On this interrupt, the application must read the OTG_DOEPTSIZx register to

determine the number of SETUP packets received and process the last received

SETUP packet.

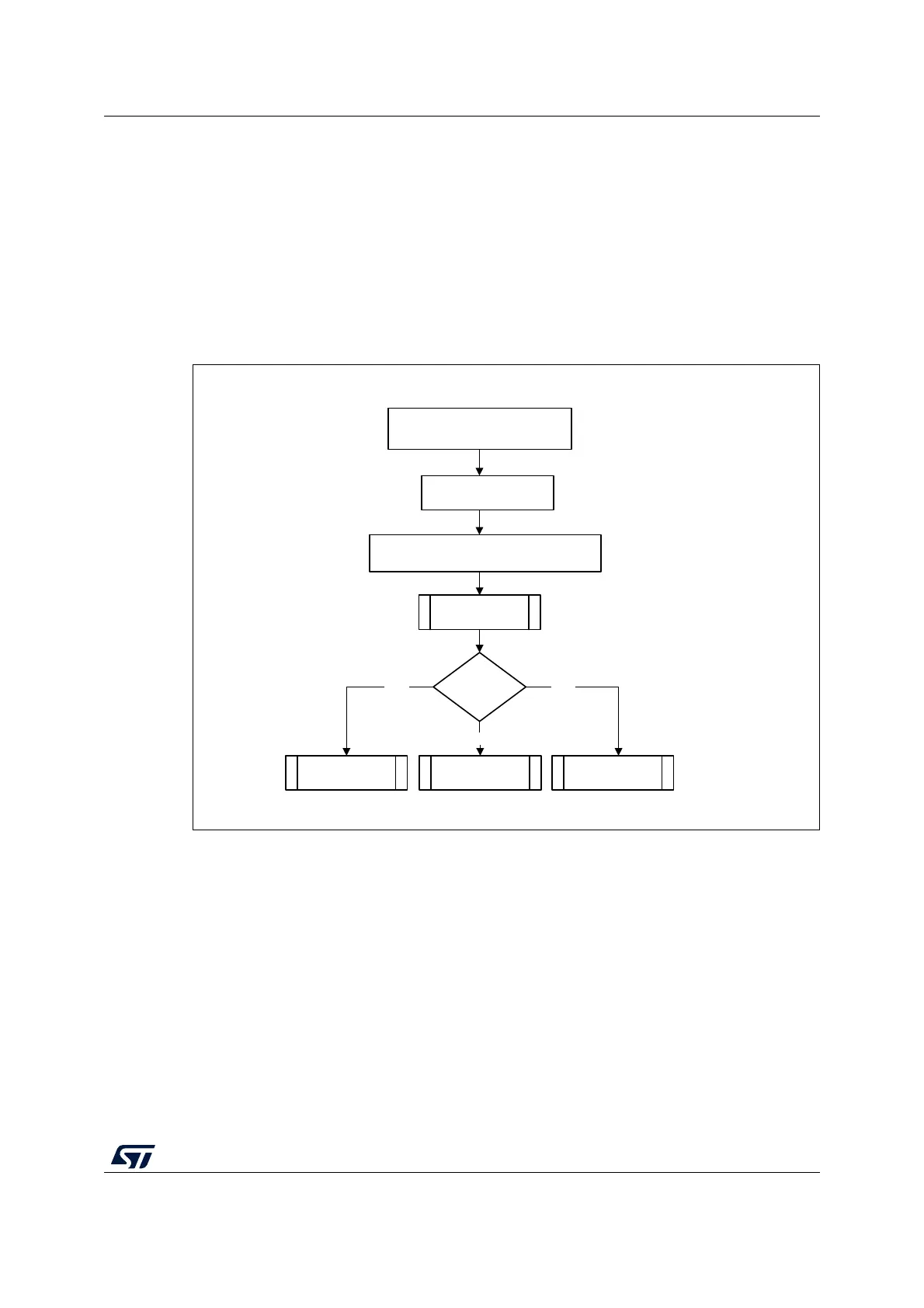

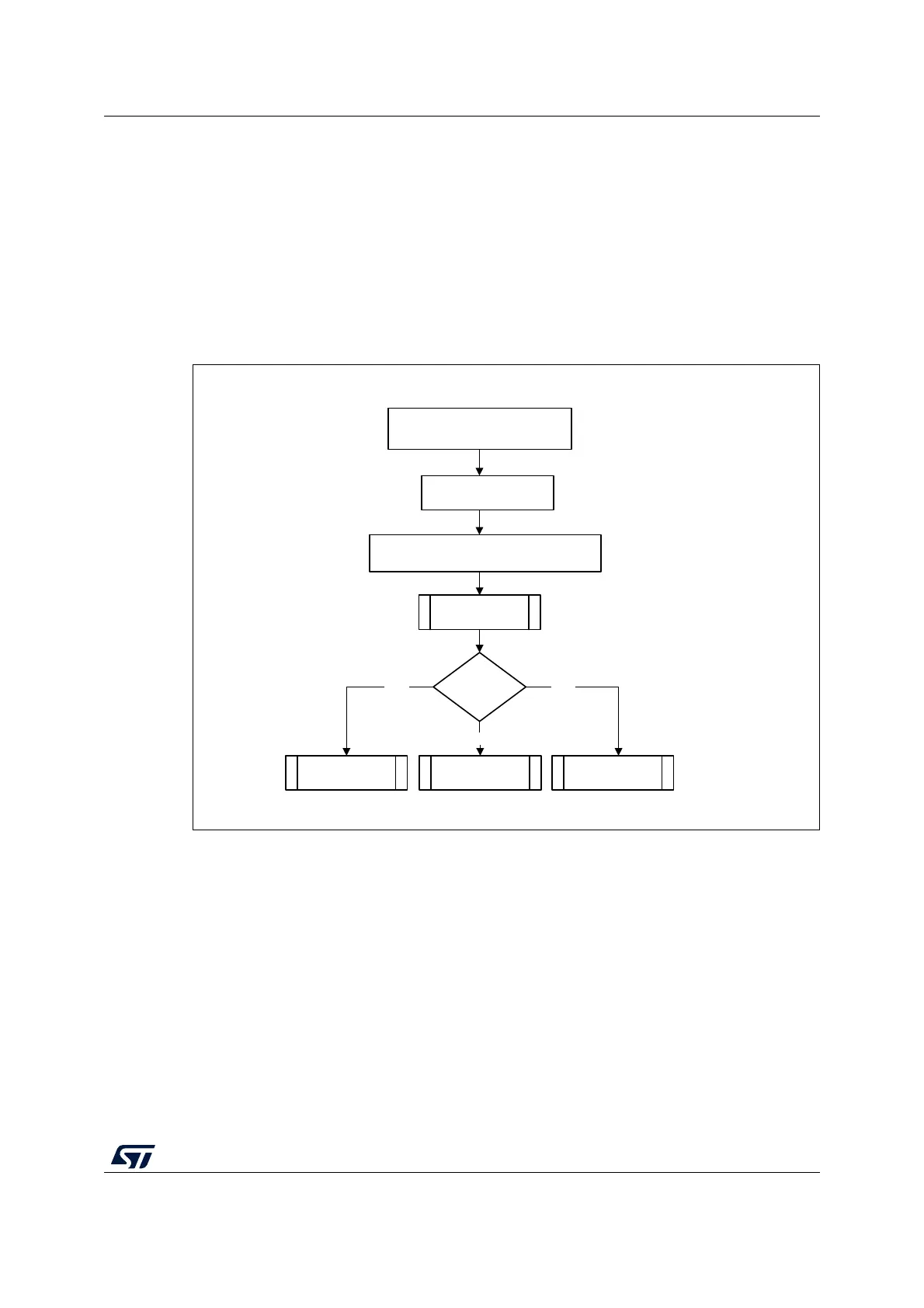

Figure 352. Processing a SETUP packet

• Handling more than three back-to-back SETUP packets

Per the USB 2.0 specification, normally, during a SETUP packet error, a host does not send

more than three back-to-back SETUP packets to the same endpoint. However, the USB 2.0

specification does not limit the number of back-to-back SETUP packets a host can send to

the same endpoint. When this condition occurs, the OTG_FS controller generates an

interrupt (B2BSTUP in OTG_DOEPINTx).

• Setting the global OUT NAK

Internal data flow:

1. When the application sets the Global OUT NAK (SGONAK bit in OTG_DCTL), the core

stops writing data, except SETUP packets, to the receive FIFO. Irrespective of the

MSv37035V1

Wait for STP in OTG_DOEPINTx

rem_supcnt=

rd_reg(OTG_DOEPTSIZx)

setup_cmd[31:0 = mem[4 – 2 * rem_supcnt]

setup_cmd[63:32] = mem[5 – 2 * rem_supcnt]

ctrl_rd/wr/2 stage

Find setup cmd type

2-stage

Read

setup_np_in_pkt

Status IN phase

rcv_out_pkt

Data OUT phase

setup_np_in_pkt

Data IN phase

Write

Loading...

Loading...