General-purpose timers (TIM9 to TIM14) RM0402

552/1163 RM0402 Rev 6

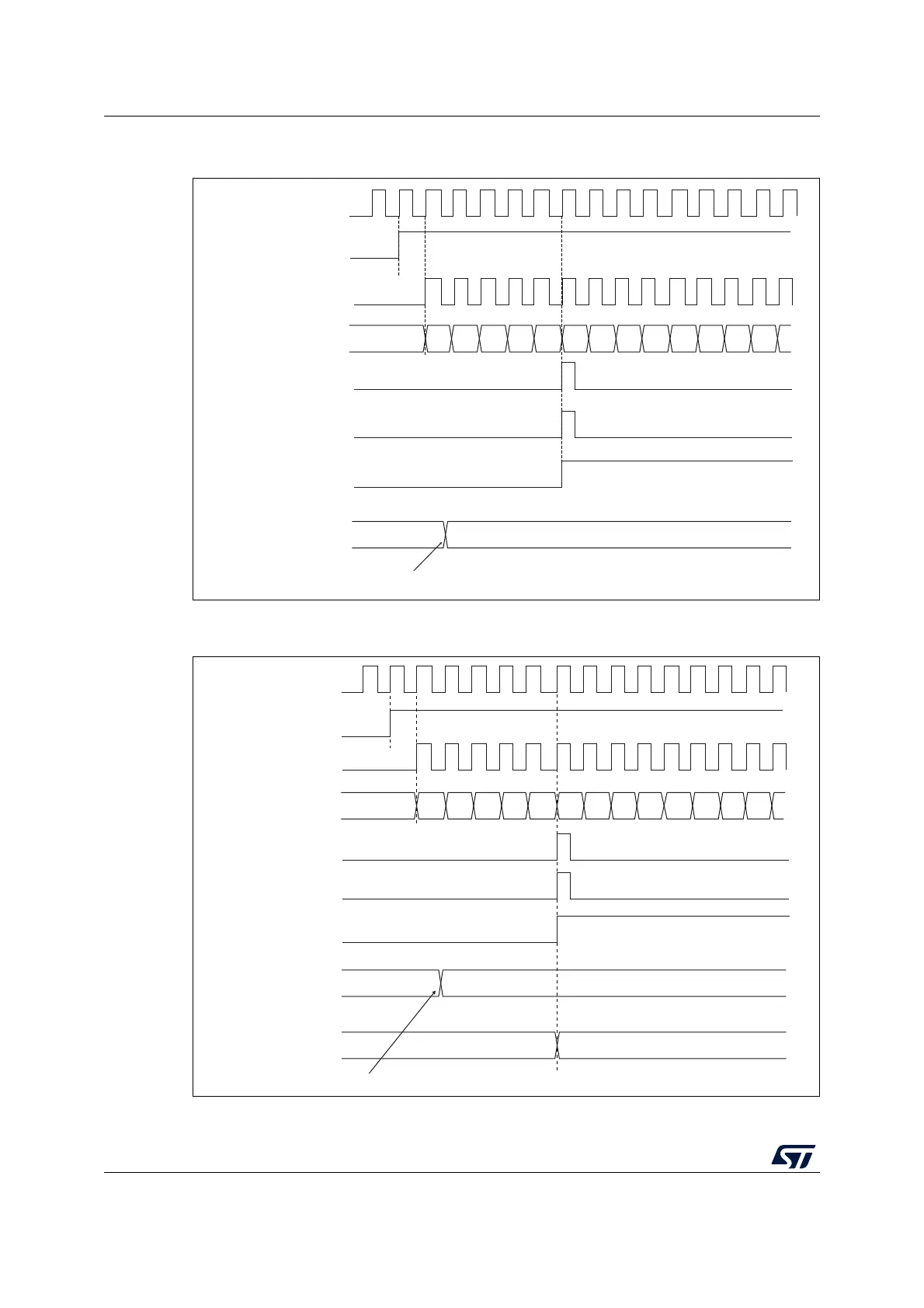

Figure 179. Counter timing diagram, update event when ARPE=0

(TIMx_ARR not preloaded)

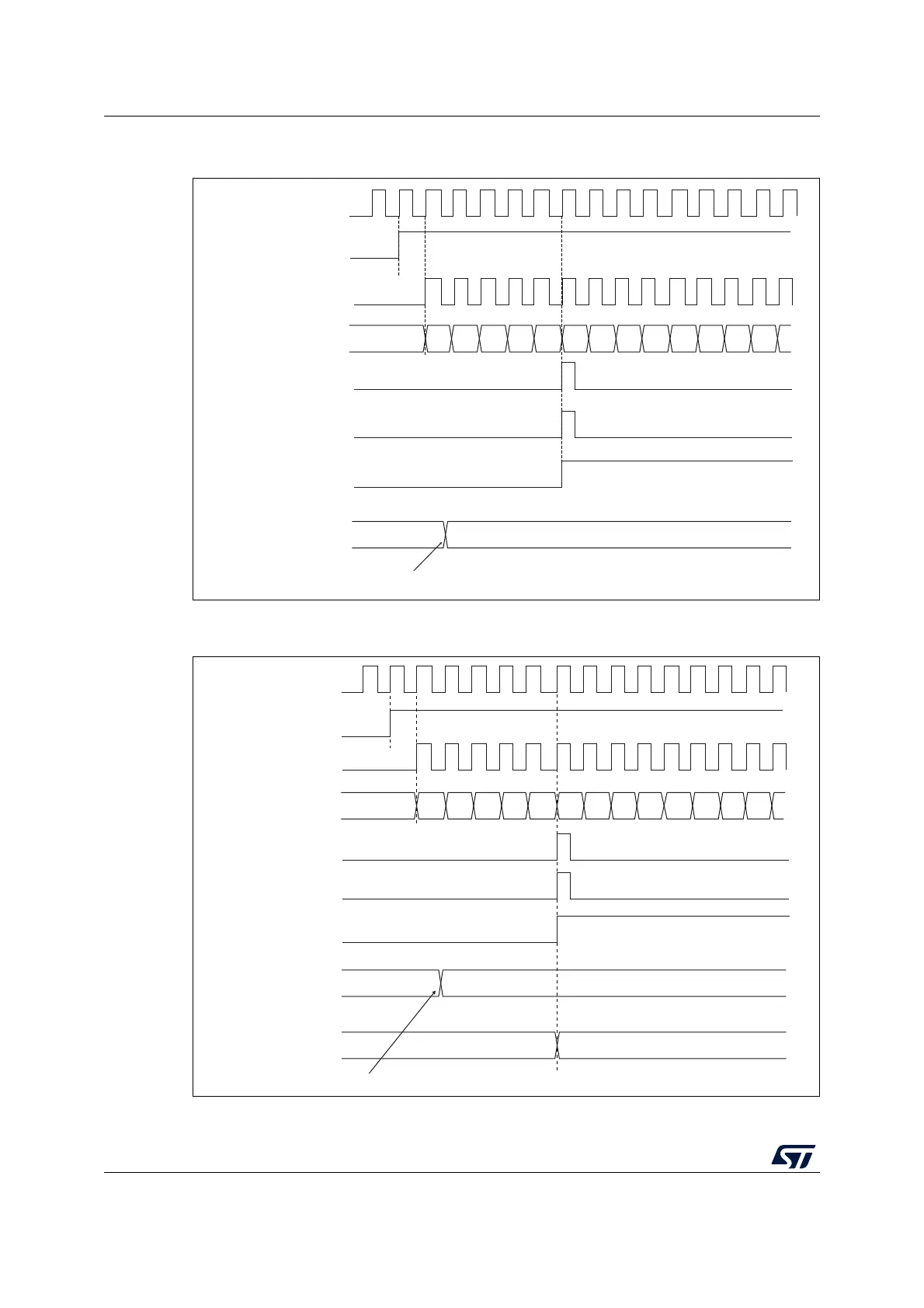

Figure 180. Counter timing diagram, update event when ARPE=1

(TIMx_ARR preloaded)

FF 36

MS31082V3

CK_PSC

Timerclock = CK_CNT

Counter register

Update event (UEV)

Counter overflow

Update interrupt flag (UIF)

00

02

03 04 05

06

0732

33

34 35

3631

01

CEN

Auto-reload preload register

Write a new value in TIMx_ARR

MS31083V2

F5

36

CK_PSC

Timerclock = CK_CNT

Counter register

Update event (UEV)

Counter overflow

Update interrupt flag

(UIF)

00

02

03 04 05

06

07F1

F2

F3 F4

F5F0

01

CEN

Auto-reload preload

register

Write a new value in TIMx_ARR

Auto-reload shadow

register

F5

36

Loading...

Loading...