Digital filter for sigma delta modulators (DFSDM) RM0402

380/1163 RM0402 Rev 6

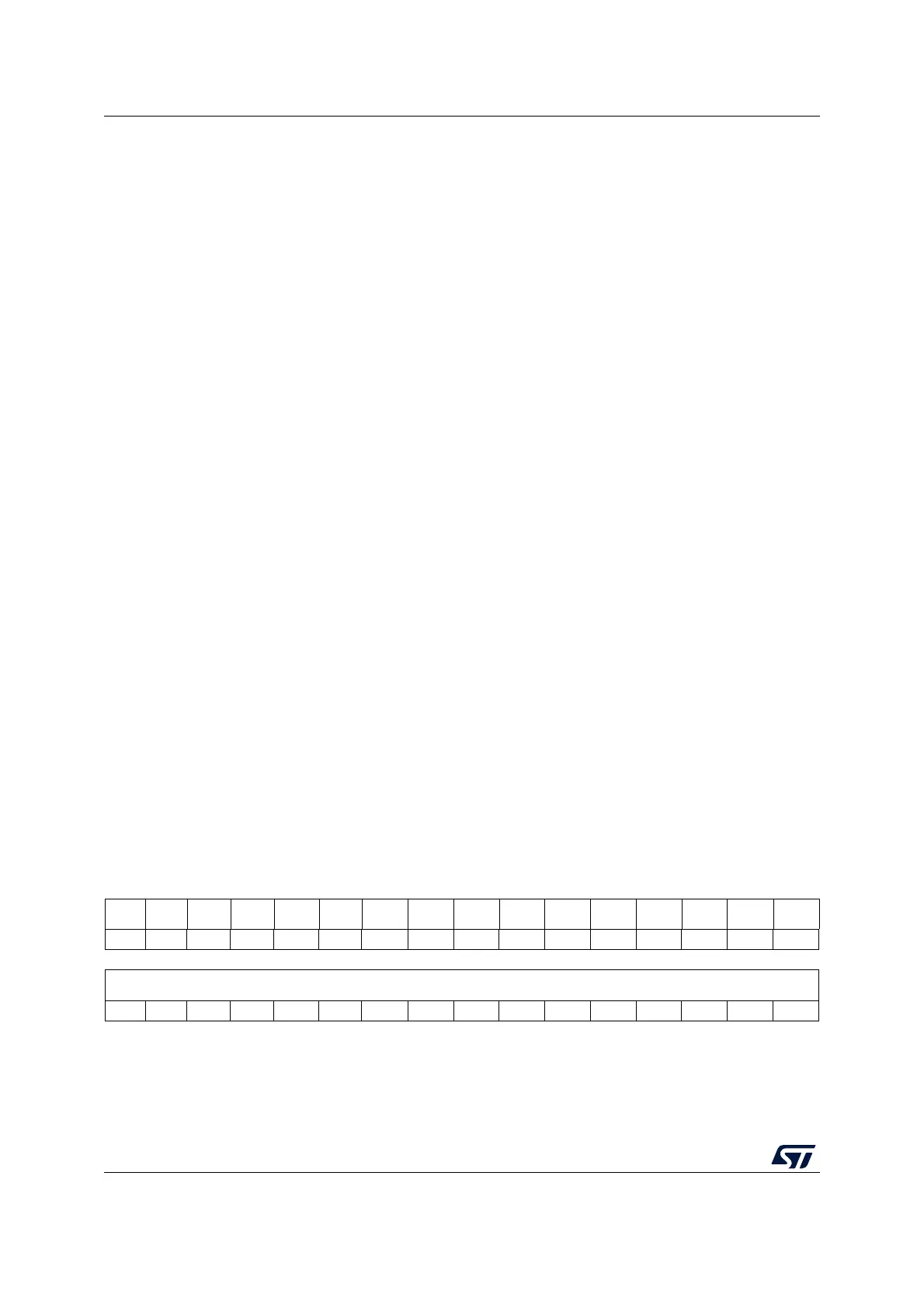

14.7.4 DFSDM channel y watchdog filter data register

(DFSDM_CHyWDATR)

This register contains the data resulting from the analog watchdog filter associated to the

input channel y.

Address offset: 0x0C + 0x20 * y, (y = 0 to 3)

Reset value: 0x0000 0000

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:22 AWFORD[1:0]: Analog watchdog Sinc filter order on channel y

0: FastSinc filter type

1: Sinc

1

filter type

2: Sinc

2

filter type

3: Sinc

3

filter type

Sinc

x

filter type transfer function:

FastSinc filter type transfer function:

This bit can be modified only when CHEN=0 (in DFSDM_CHyCFGR1 register).

Bit 21 Reserved, must be kept at reset value.

Bits 20:16 AWFOSR[4:0]: Analog watchdog filter oversampling ratio (decimation rate) on channel y

0 - 31: Defines the length of the Sinc type filter in the range 1 - 32 (AWFOSR + 1). This number is

also the decimation ratio of the analog data rate.

This bit can be modified only when CHEN=0 (in DFSDM_CHyCFGR1 register).

Note: If AWFOSR = 0 then the filter has no effect (filter bypass).

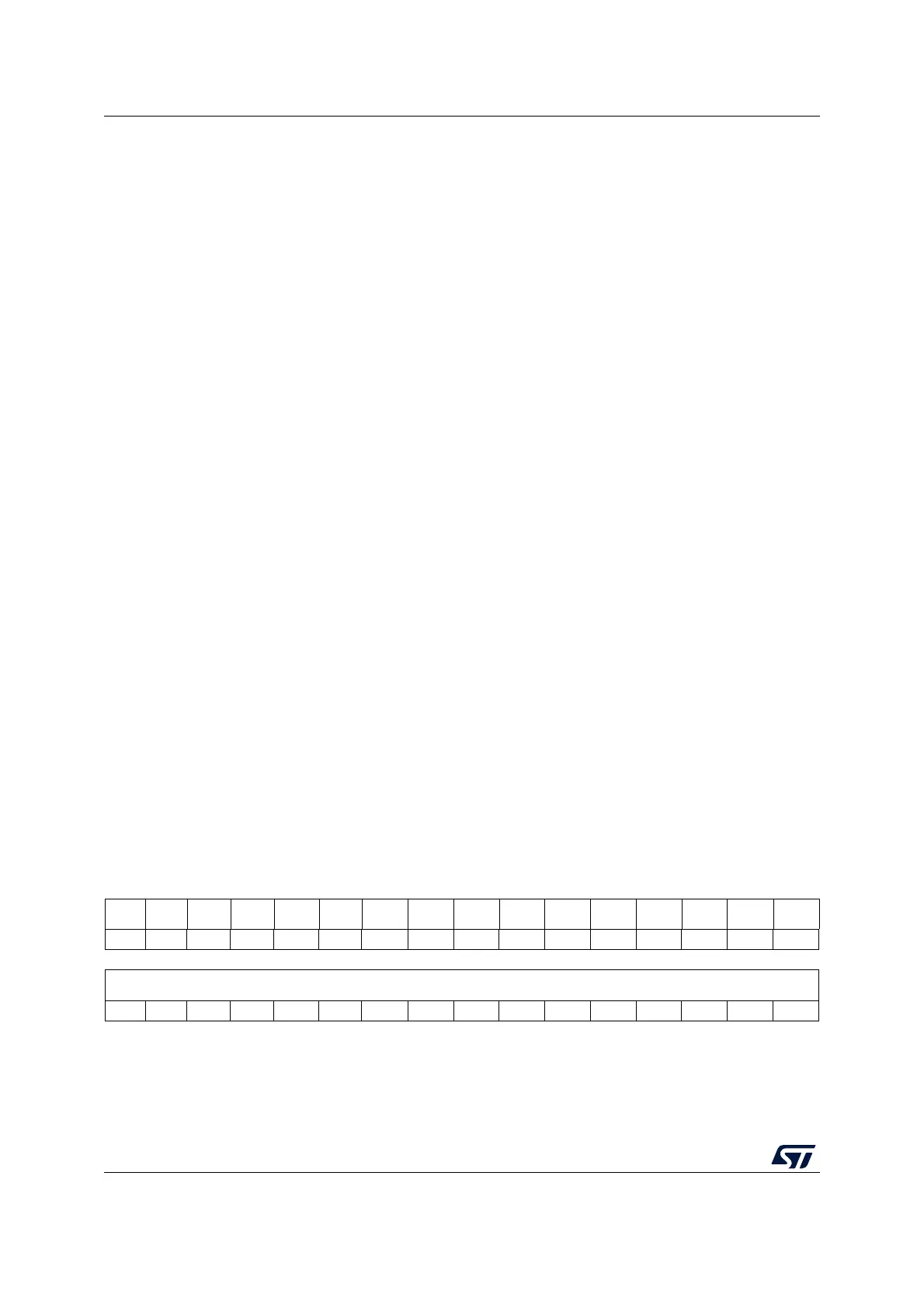

Bits 15:12 BKSCD[3:0]: Break signal assignment for short-circuit detector on channel y

BKSCD[i] = 0: Break i signal not assigned to short-circuit detector on channel y

BKSCD[i] = 1: Break i signal assigned to short-circuit detector on channel y

Bits 11:8 Reserved, must be kept at reset value.

Bits 7:0 SCDT[7:0]: short-circuit detector threshold for channel y

These bits are written by software to define the threshold counter for the short-circuit detector. If this

value is reached, then a short-circuit detector event occurs on a given channel.

Hz()

1z

FOSR–

–

1z

1–

–

-----------------------------

x

=

Hz()

1z

FOSR–

–

1z

1–

–

-----------------------------

2

1z

2FOSR⋅()–

+()⋅=

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

WDATA[15:0]

rrrrrrrrrrrrrrrr

Loading...

Loading...