RM0402 Rev 6 361/1163

RM0402 Digital filter for sigma delta modulators (DFSDM)

400

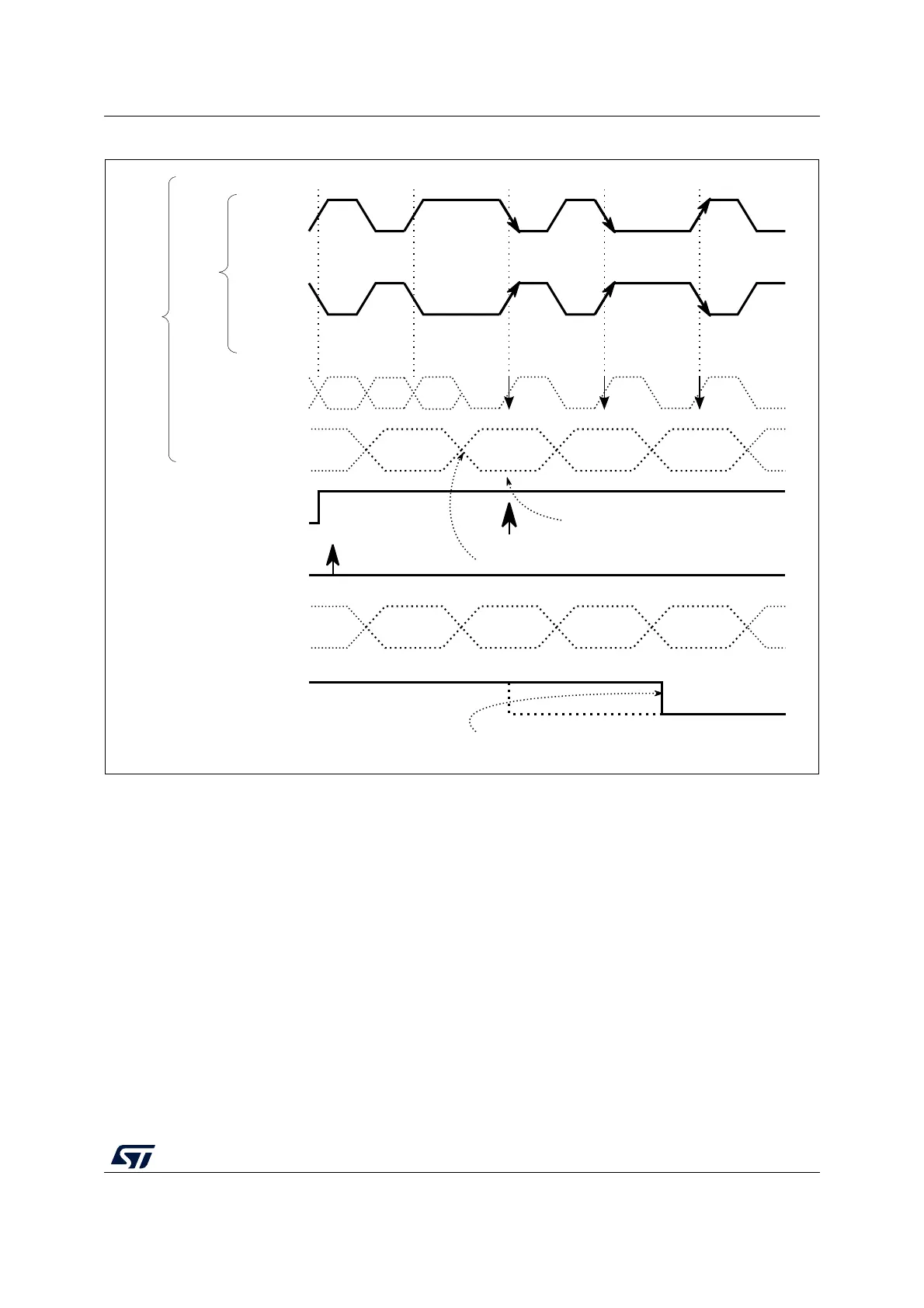

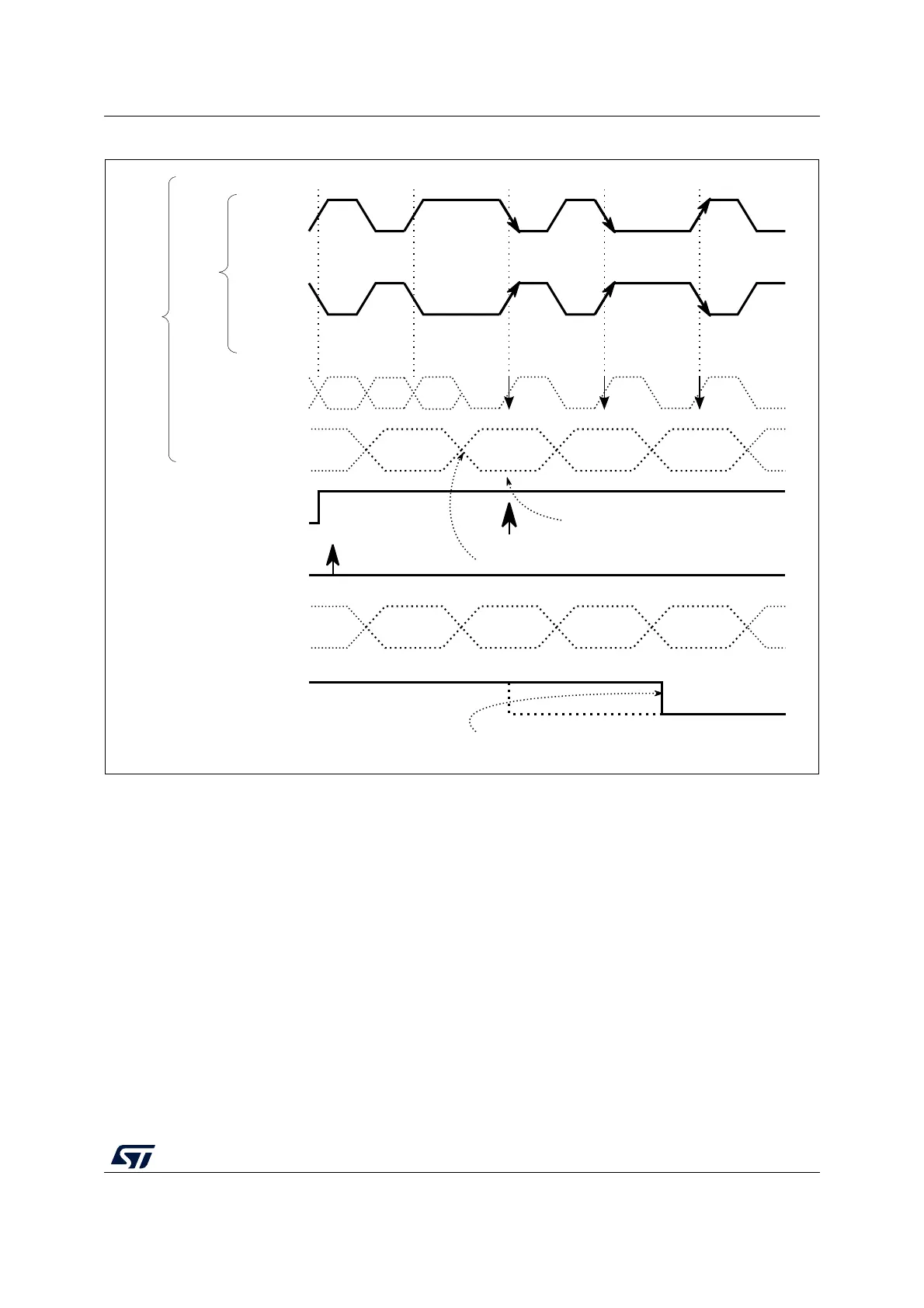

Figure 72. First conversion for Manchester coding (Manchester synchronization)

External serial clock frequency measurement

The measuring of a channel serial clock input frequency provides a real data rate from an

external Σ∆ modulator, which is important for application purposes.

An external serial clock input frequency can be measured by a timer counting DFSDM

clocks (f

DFSDMCLK

) during one conversion duration. The counting starts at the first input data

clock after a conversion trigger (regular or injected) and finishes by last input data clock

before conversion ends (end of conversion flag is set). Each conversion duration (time

between first serial sample and last serial sample) is updated in counter CNVCNT[27:0] in

register DFSDM_FLTxCNVTIMR when the conversion finishes (JEOCF=1 or REOCF=1).

The user can then compute the data rate according to the digital filter settings (FORD,

FOSR, IOSR, FAST). The external serial frequency measurement is stopped only if the filter

is bypassed (FOSR=0, only integrator is active, CNVCNT[27:0]=0 in

DFSDM_FLTxCNVTIMR register).

In case of parallel data input (Section 14.4.6: Parallel data inputs) the measured frequency

is the average input data rate during one conversion.

MS30769V2

recovered clock

SITP = 2

DATINy

SITP = 3

Manchester timing

data from

modulator

11000

CHEN

first data bit toggle - end of Manchester synchronization

first conversion

start trigger

recovered data

110??

real start of first conversion

CKABF[y]

clearing of CKABF[y] flag by software polling

Loading...

Loading...