RM0402 Rev 6 607/1163

RM0402 Independent watchdog (IWDG)

610

20.4 IWDG registers

Refer to Section 1.2 on page 45 for a list of abbreviations used in register descriptions.

The peripheral registers have to be accessed by half-words (16 bits) or words (32 bits).

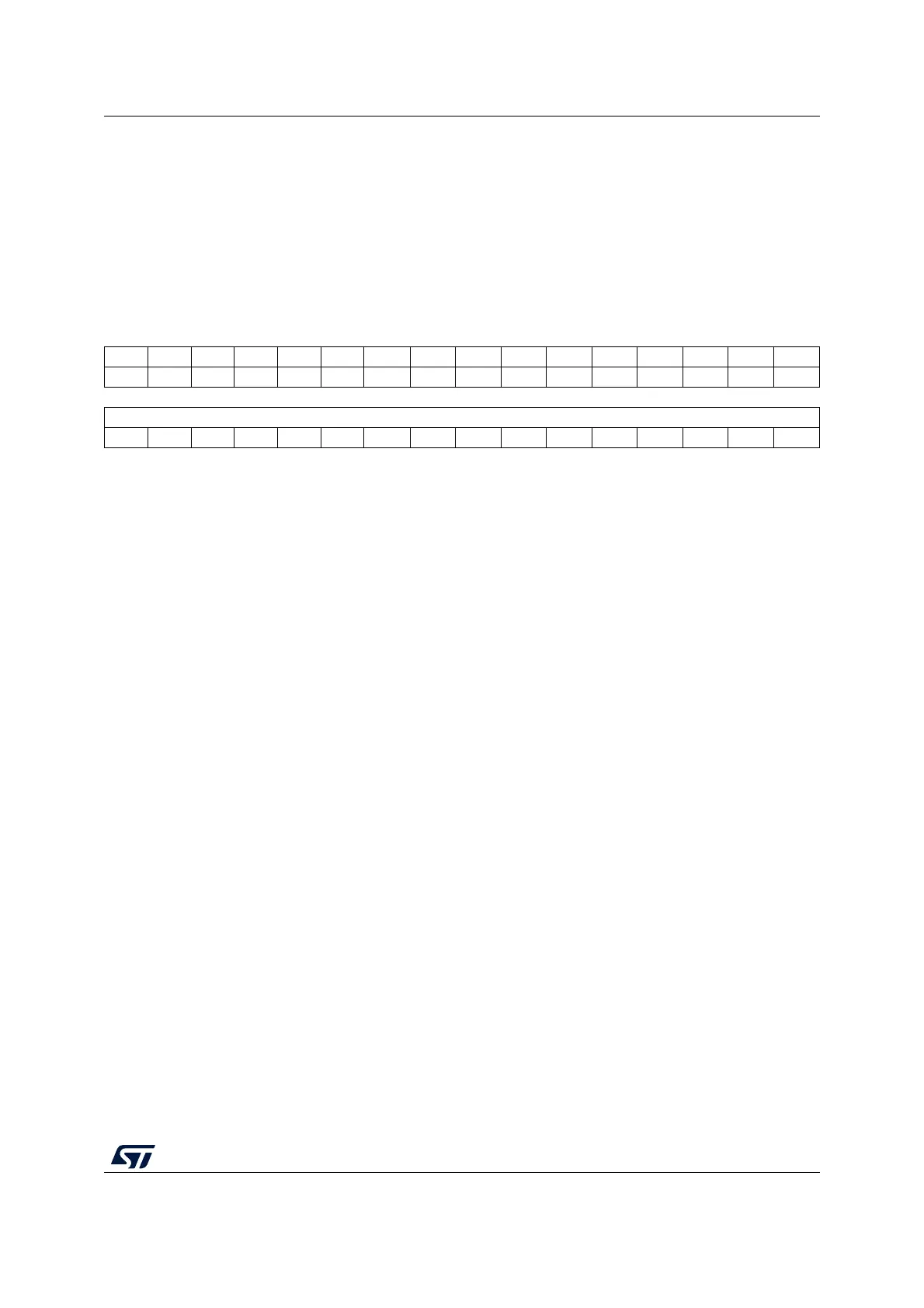

20.4.1 Key register (IWDG_KR)

Address offset: 0x00

Reset value: 0x0000 0000 (reset by Standby mode)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

KEY[15:0]

w w w w w w w w w w w w w w w w

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 KEY[15:0]: Key value (write only, read 0000h)

These bits must be written by software at regular intervals with the key value AAAAh,

otherwise the watchdog generates a reset when the counter reaches 0.

Writing the key value 5555h to enable access to the IWDG_PR and IWDG_RLR registers

(see Section 20.3.2)

Writing the key value CCCCh starts the watchdog (except if the hardware watchdog option is

selected)

Loading...

Loading...