RM0402 Rev 6 379/1163

RM0402 Digital filter for sigma delta modulators (DFSDM)

400

14.7.2 DFSDM channel y configuration register (DFSDM_CHyCFGR2)

This register specifies the parameters used by channel y.

Address offset: 0x04 + 0x20 * y, (y = 0 to 3)

Reset value: 0x0000 0000

14.7.3 DFSDM channel y analog watchdog and short-circuit detector register

(DFSDM_CHyAWSCDR)

Short-circuit detector and analog watchdog settings for channel y.

Address offset: 0x08 + 0x20 * y, (y = 0 to 3)

Reset value: 0x0000 0000

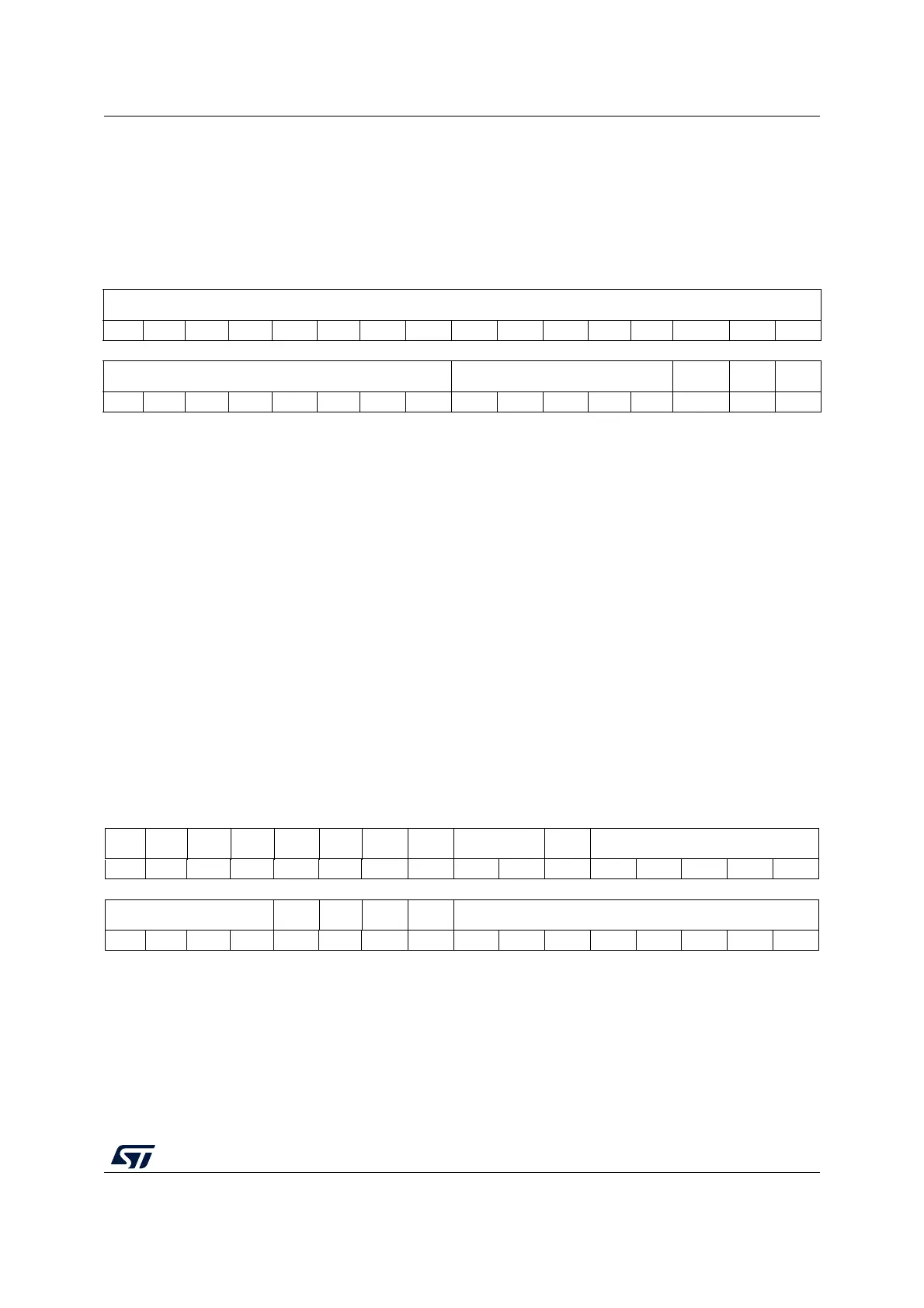

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

OFFSET[23:8]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET[7:0] DTRBS[4:0] Res. Res. Res.

rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:8 OFFSET[23:0]: 24-bit calibration offset for channel y

For channel y, OFFSET is applied to the results of each conversion from this channel.

This value is set by software.

Bits 7:3 DTRBS[4:0]: Data right bit-shift for channel y

0-31: Defines the shift of the data result coming from the integrator - how many bit shifts to the right

will be performed to have final results. Bit-shift is performed before offset correction. The data shift is

rounding the result to nearest integer value. The sign of shifted result is maintained (to have valid

24-bit signed format of result data).

This value can be modified only when CHEN=0 (in DFSDM_CHyCFGR1 register).

Bits 2:0 Reserved, must be kept at reset value.

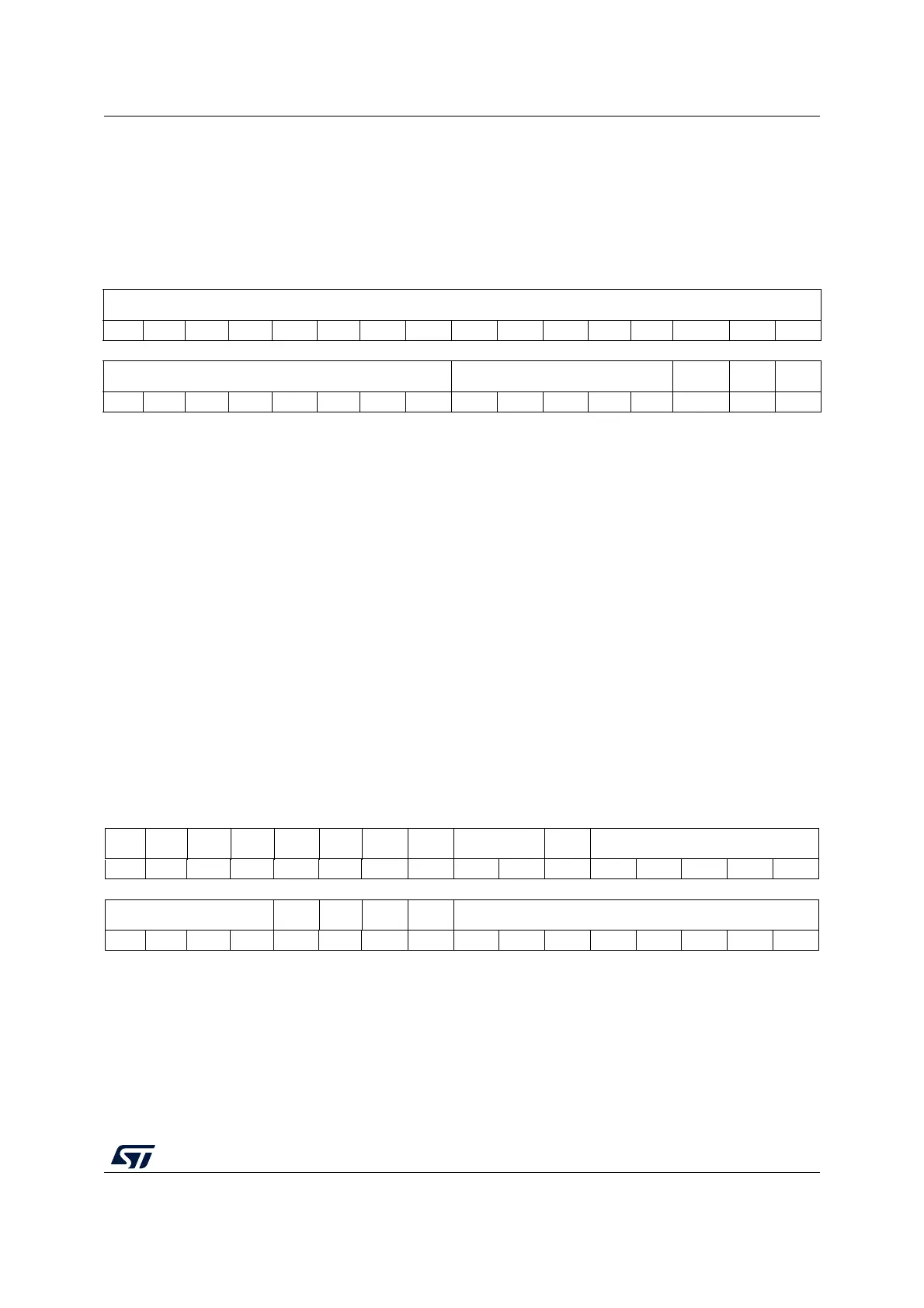

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. AWFORD[1:0] Res. AWFOSR[4:0]

rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

BKSCD[3:0] Res. Res. Res. Res. SCDT[7:0]

rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...