RM0402 Rev 6 251/1163

RM0402 Flexible static memory controller (FSMC)

287

and synchronous accesses depending on the CCKEN bit configuration in the FSMC_BCR1

register:

• If the CCLKEN bit is reset, the FSMC generates the clock (CLK) only during

synchronous accesses (Read/write transactions).

• If the CCLKEN bit is set, the FSMC generates a continuous clock during asynchronous

and synchronous accesses. To generate the FSMC_CLK continuous clock, Bank 1

must be configured in Synchronous mode (see Section 11.6.6: NOR/PSRAM controller

registers). Since the same clock is used for all synchronous memories, when a

continuous output clock is generated and synchronous accesses are performed, the

AHB data size has to be the same as the memory data width (MWID) otherwise the

FSMC_CLK frequency is changed depending on AHB data transaction (refer to

Section 11.6.5: Synchronous transactions for FSMC_CLK divider ratio formula).

The size of each bank is fixed and equal to 64 Mbytes. Each bank is configured through

dedicated registers (see

Section 11.6.6: NOR/PSRAM controller registers).

The programmable memory parameters include access times (see Table 44) and support

for wait management (for PSRAM and NOR Flash accessed in Burst mode).

11.6.1 External memory interface signals

Table 45, Table 46 and Table 47 list the signals that are typically used to interface with NOR

Flash memory, SRAM and PSRAM.

Note: The prefix “N” identifies the signals that are active low.

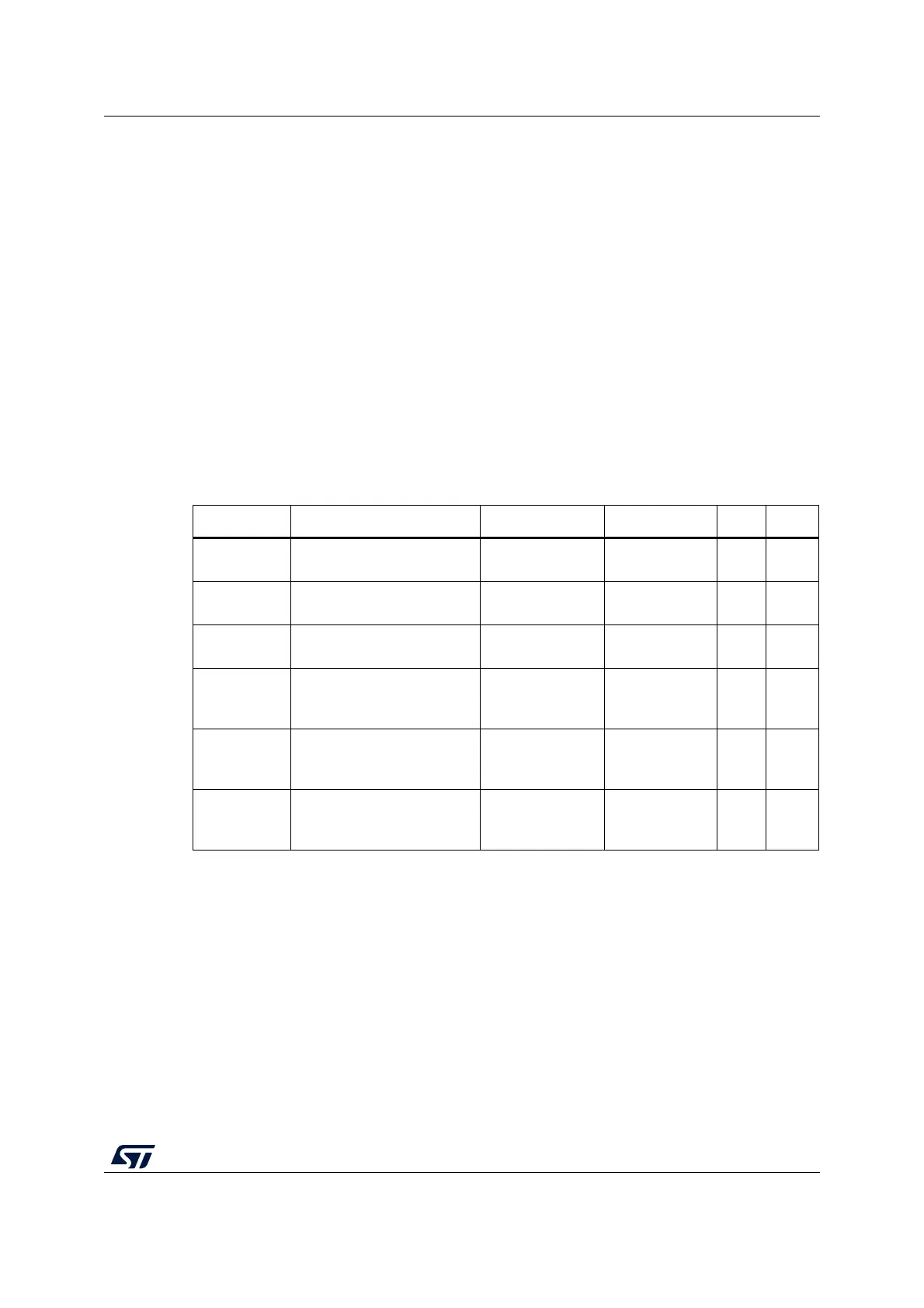

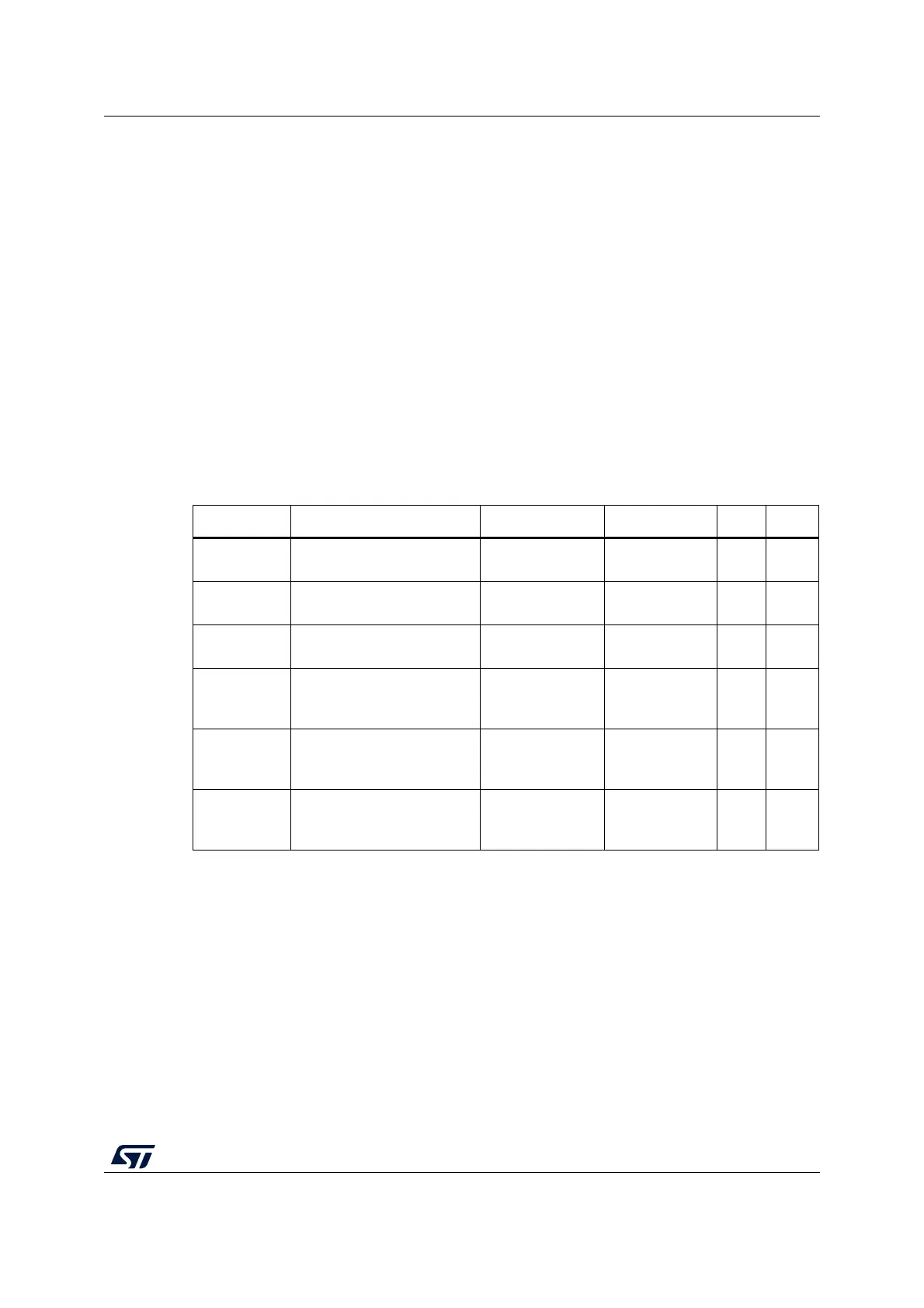

Table 44. Programmable NOR/PSRAM access parameters

Parameter Function Access mode Unit Min. Max.

Address

setup

Duration of the address

setup phase

Asynchronous

AHB clock cycle

(HCLK)

015

Address hold

Duration of the address hold

phase

Asynchronous,

muxed I/Os

AHB clock cycle

(HCLK)

115

Data setup

Duration of the data setup

phase

Asynchronous

AHB clock cycle

(HCLK)

1256

Bust turn

Duration of the bus

turnaround phase

Asynchronous and

synchronous read

/ write

AHB clock cycle

(HCLK)

015

Clock divide

ratio

Number of AHB clock cycles

(HCLK) to build one memory

clock cycle (CLK)

Synchronous

AHB clock cycle

(HCLK)

2 16

Data latency

Number of clock cycles to

issue to the memory before

the first data of the burst

Synchronous

Memory clock

cycle (CLK)

2 17

Loading...

Loading...