RM0402 Rev 6 537/1163

RM0402 General-purpose timers (TIM2 to TIM5)

544

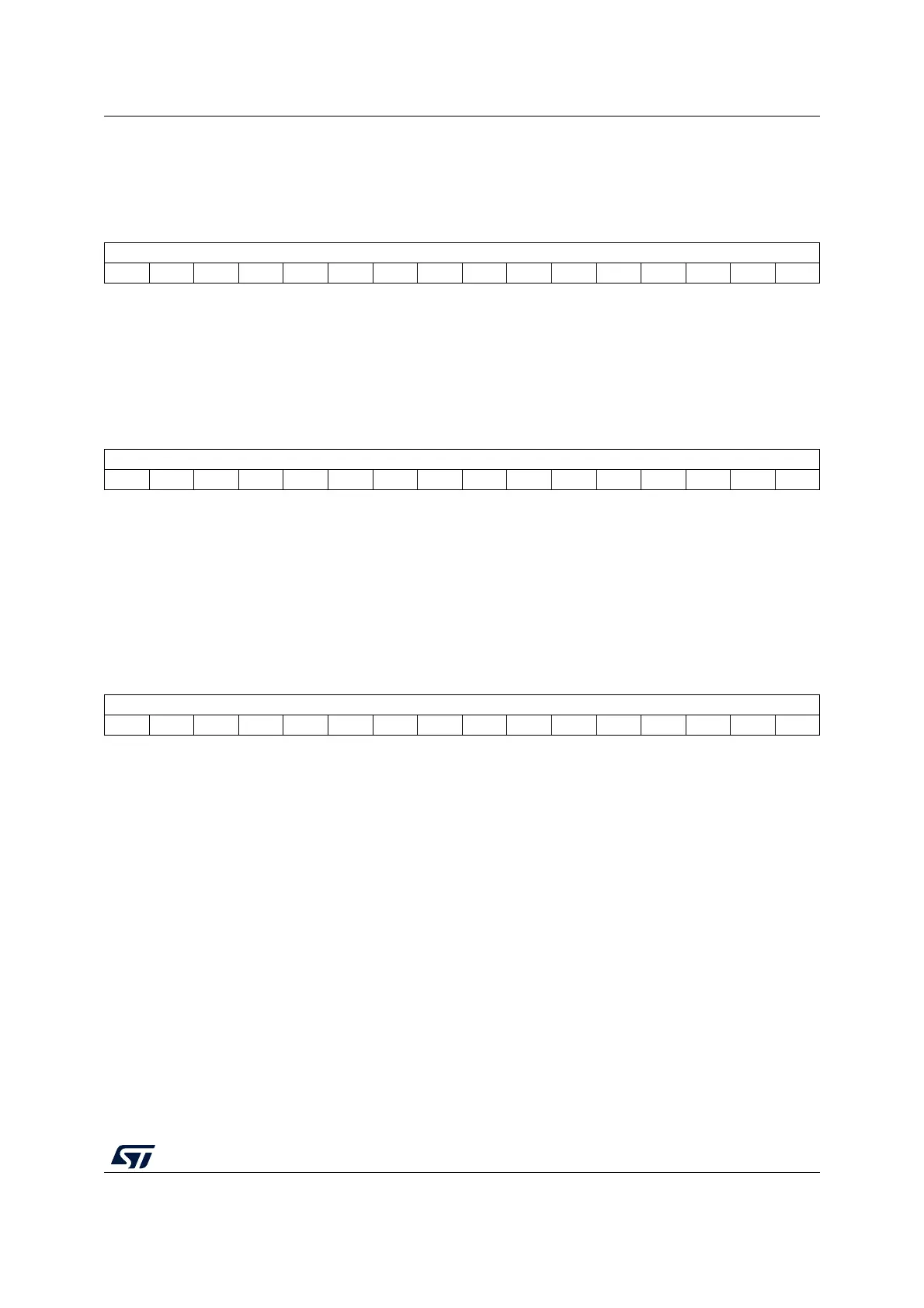

17.4.10 TIMx counter (TIMx_CNT)

Address offset: 0x24

Reset value: 0x0000

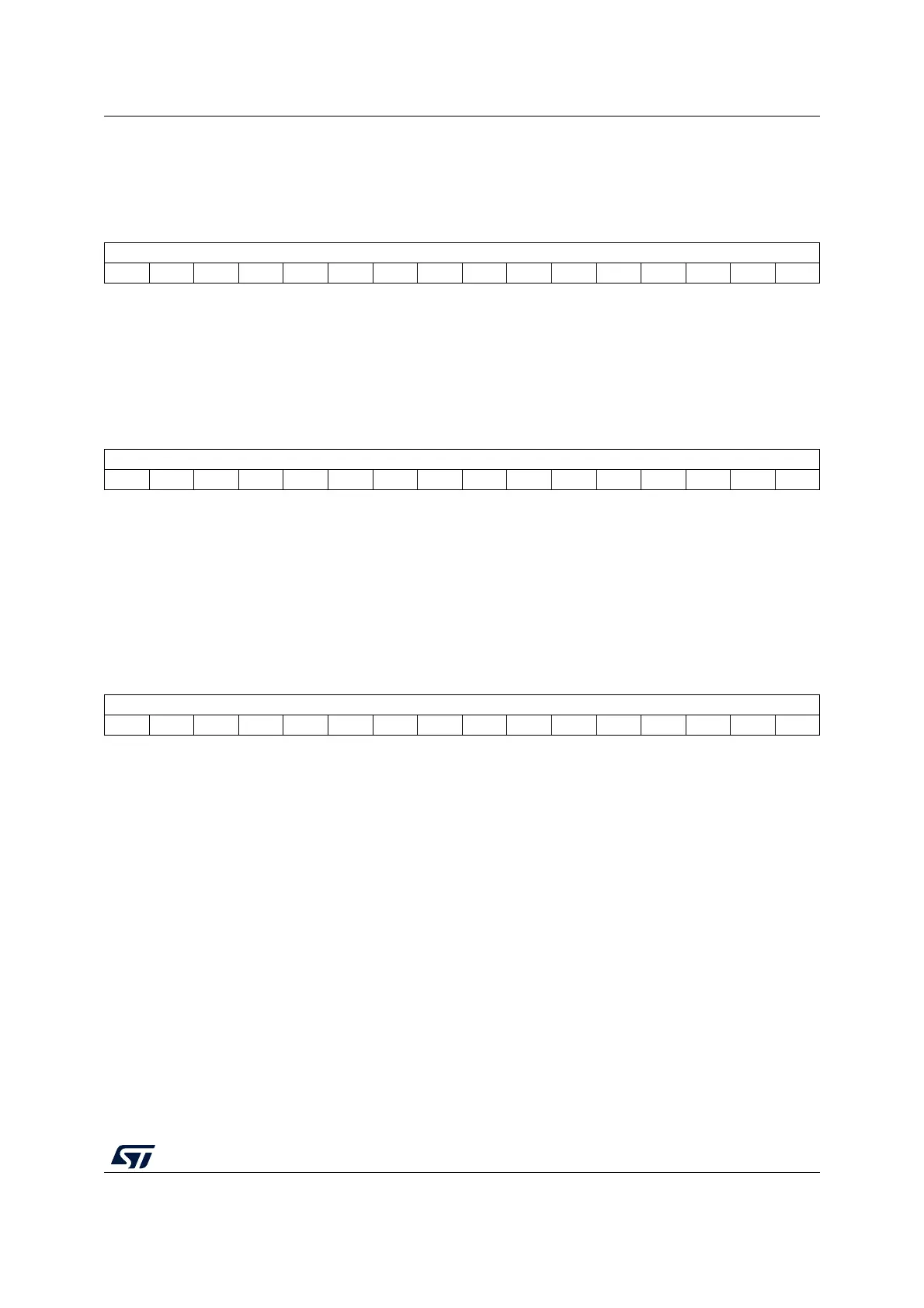

17.4.11 TIMx prescaler (TIMx_PSC)

Address offset: 0x28

Reset value: 0x0000

17.4.12 TIMx auto-reload register (TIMx_ARR)

Address offset: 0x2C

Reset value: 0x0000

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CNT[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0 CNT[15:0]: Counter value

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PSC[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0 PSC[15:0]: Prescaler value

The counter clock frequency CK_CNT is equal to f

CK_PSC

/ (PSC[15:0] + 1).

PSC contains the value to be loaded in the active prescaler register at each update event.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ARR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0 ARR[15:0]: Auto-reload value

ARR is the value to be loaded in the actual auto-reload register.

Refer to the Section 17.3.1: Time-base unit on page 485 for more details about ARR update

and behavior.

The counter is blocked while the auto-reload value is null.

Loading...

Loading...