RM0402 Rev 6 95/1163

RM0402 Power controller (PWR)

108

5.3.3 Sleep mode

Entering Sleep mode

The Sleep mode is entered according to Entering low-power mode, when the SLEEPDEEP

bit in the Cortex

®

-M4 with FPU System Control register is cleared.

Refer to Table 16 and Table 17 for details on how to enter Sleep mode.

Note: All interrupt pending bits must be cleared before the sleep mode entry.

Exiting Sleep mode

The Sleep mode is exited according to Exiting low-power mode.

Refer to Table 16 and Table 17 for more details on how to exit Sleep mode.

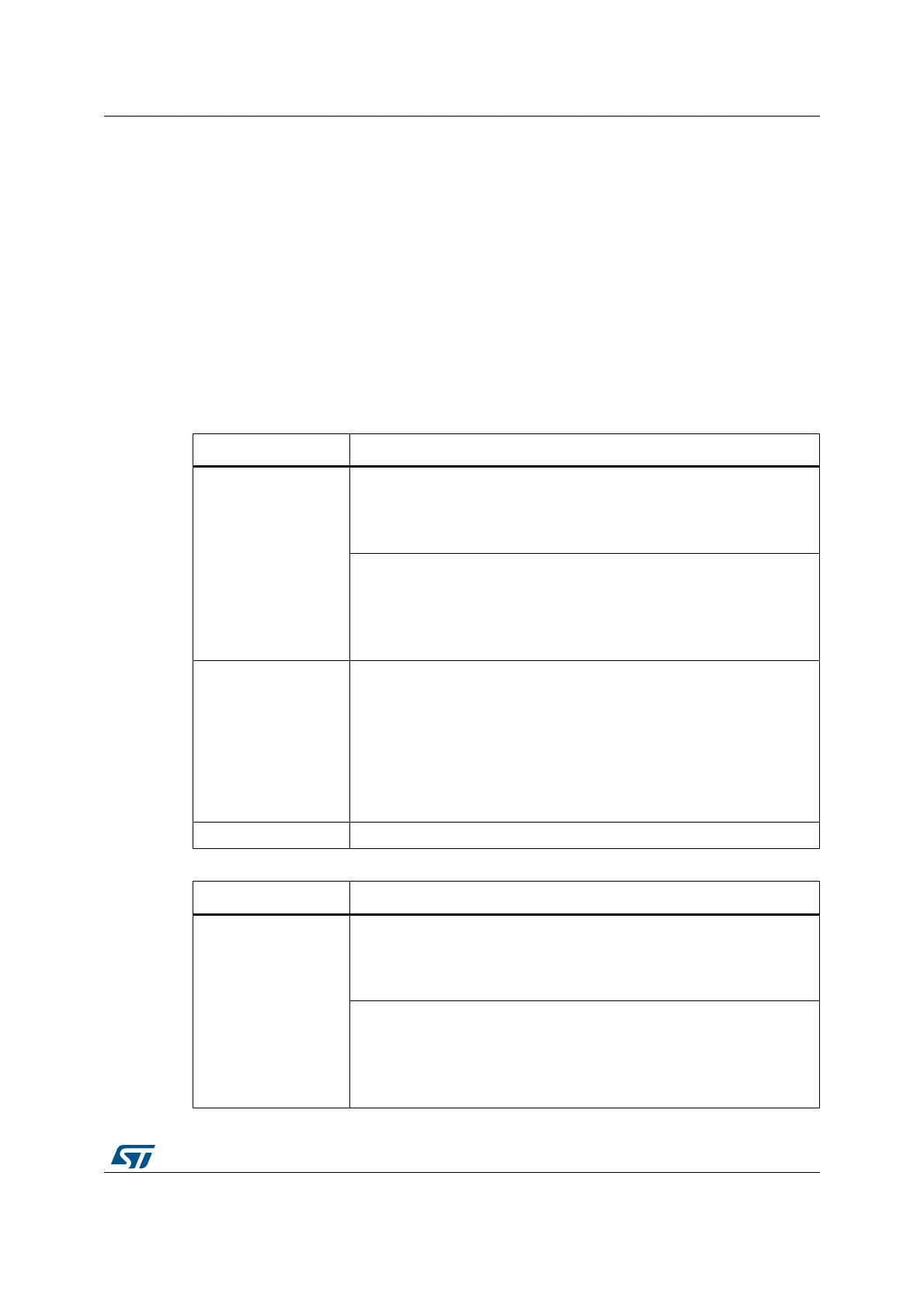

Table 16. Sleep-now entry and exit

Sleep-now mode Description

Mode entry

WFI (Wait for Interrupt) or WFE (Wait for Event) while:

– SLEEPDEEP = 0, and

– No interrupt (for WFI) or event (for WFE) is pending.

Refer to the Cortex

®

-M4 with FPU System Control register.

On Return from ISR while:

– SLEEPDEEP = 0 and

– SLEEPONEXIT = 1,

– No interrupt is pending.

Refer to the Cortex

®

-M4 with FPU System Control register.

Mode exit

If WFI or Return from ISR was used for entry:

Interrupt: Refer to Table 40: Vector table for STM32F412xx

If WFE was used for entry and SEVONPEND = 0

Wakeup event: Refer to Section 10.2.3: Wakeup event management

f WFE was used for entry and SEVONPEND = 1

Interrupt even when disabled in NVIC: refer to Table 40: Vector table for

STM32F412xx or Wakeup event (see Section 10.2.3: Wakeup event

management).

Wakeup latency None

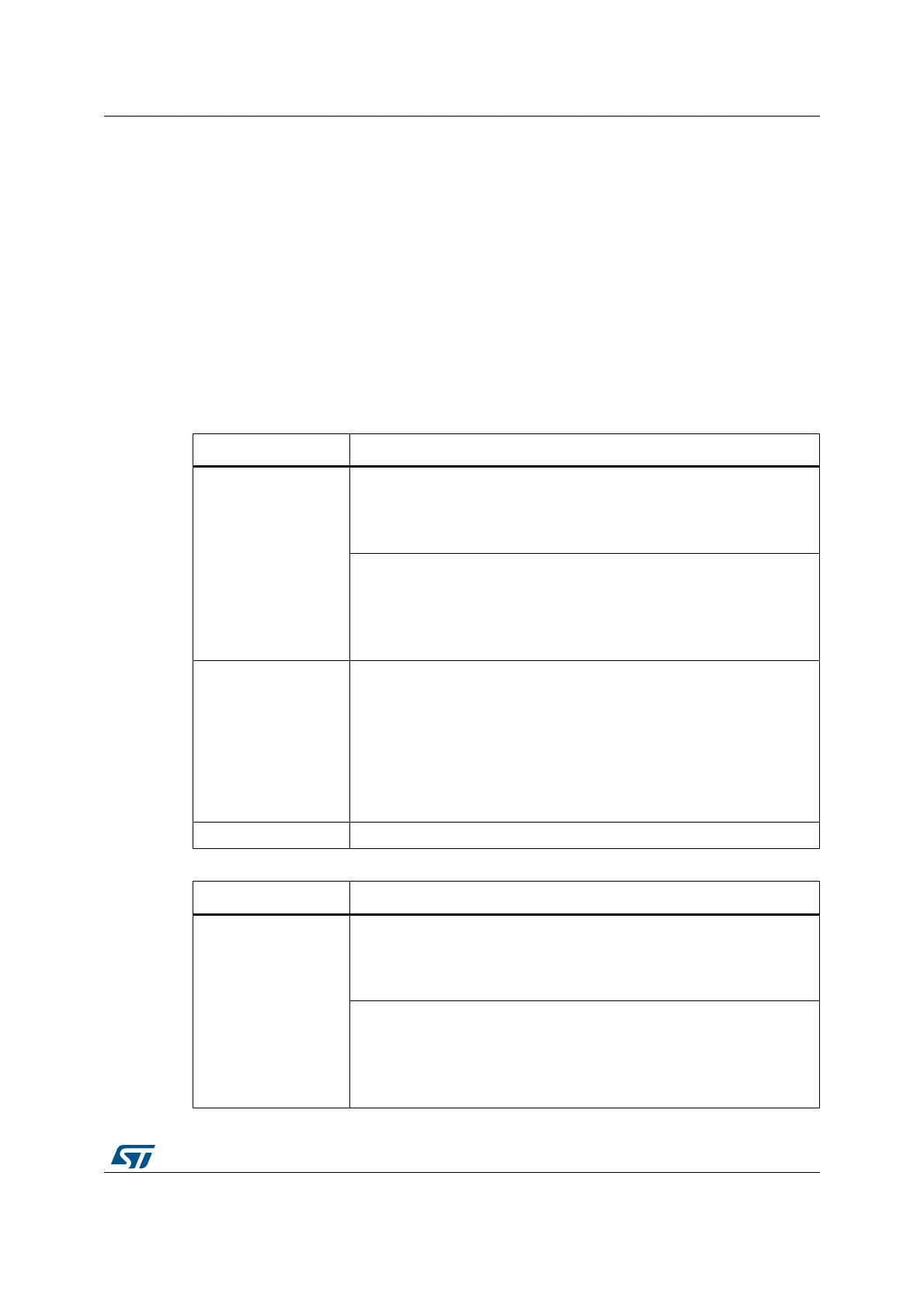

Table 17. Sleep-on-exit entry and exit

Sleep-on-exit Description

Mode entry

WFI (Wait for Interrupt) or WFE (Wait for Event) while:

– SLEEPDEEP = 0, and

– No interrupt (for WFI) or event (for WFE) is pending.

Refer to the Cortex

®

-M4 with FPU System Control register.

On Return from ISR while:

– SLEEPDEEP = 0, and

– SLEEPONEXIT = 1, and

– No interrupt is pending.

Refer to the Cortex

®

-M4 with FPU System Control register.

Loading...

Loading...