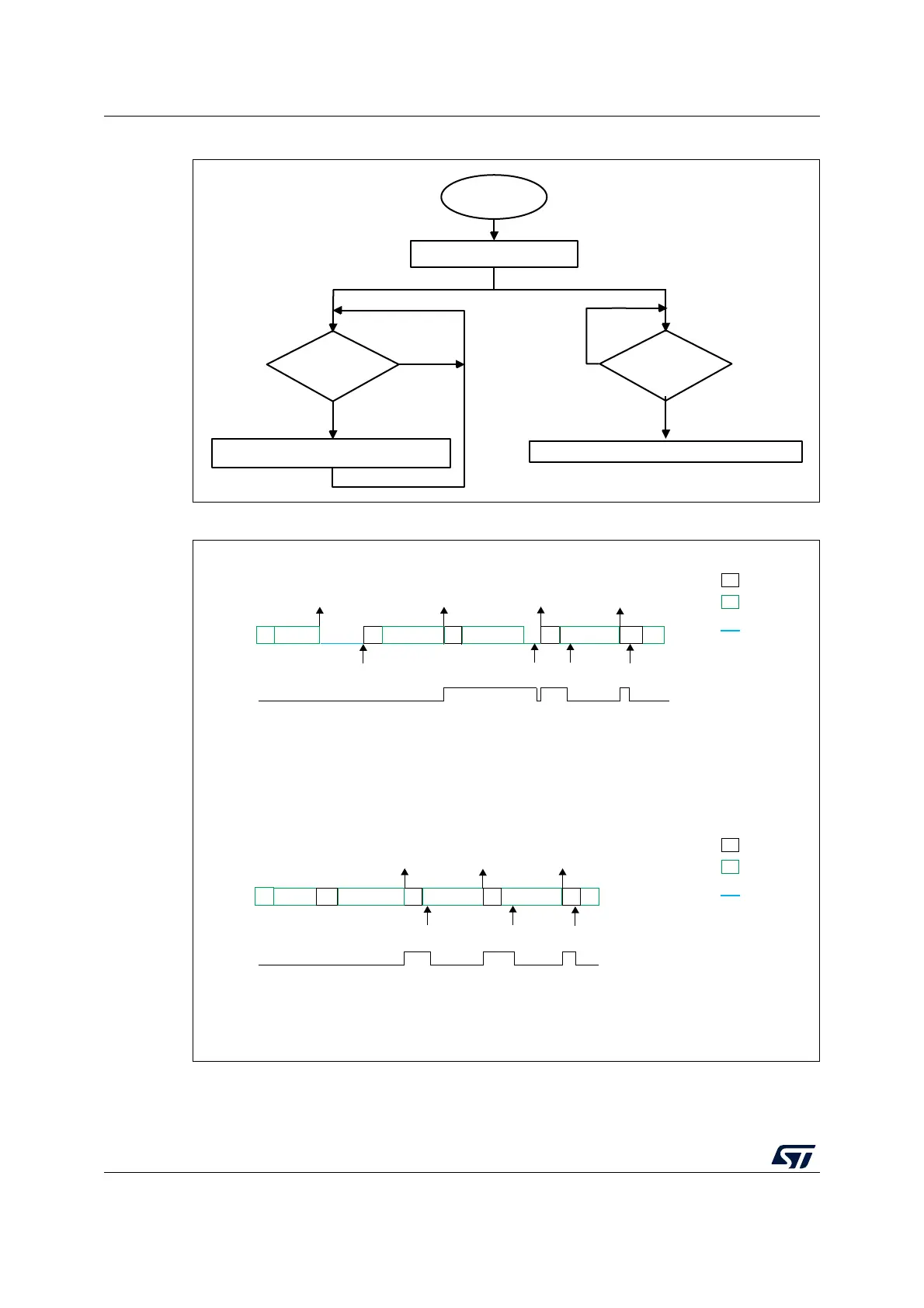

Figure 219. Transfer sequence flowchart for slave receiver with NOSTRETCH=1

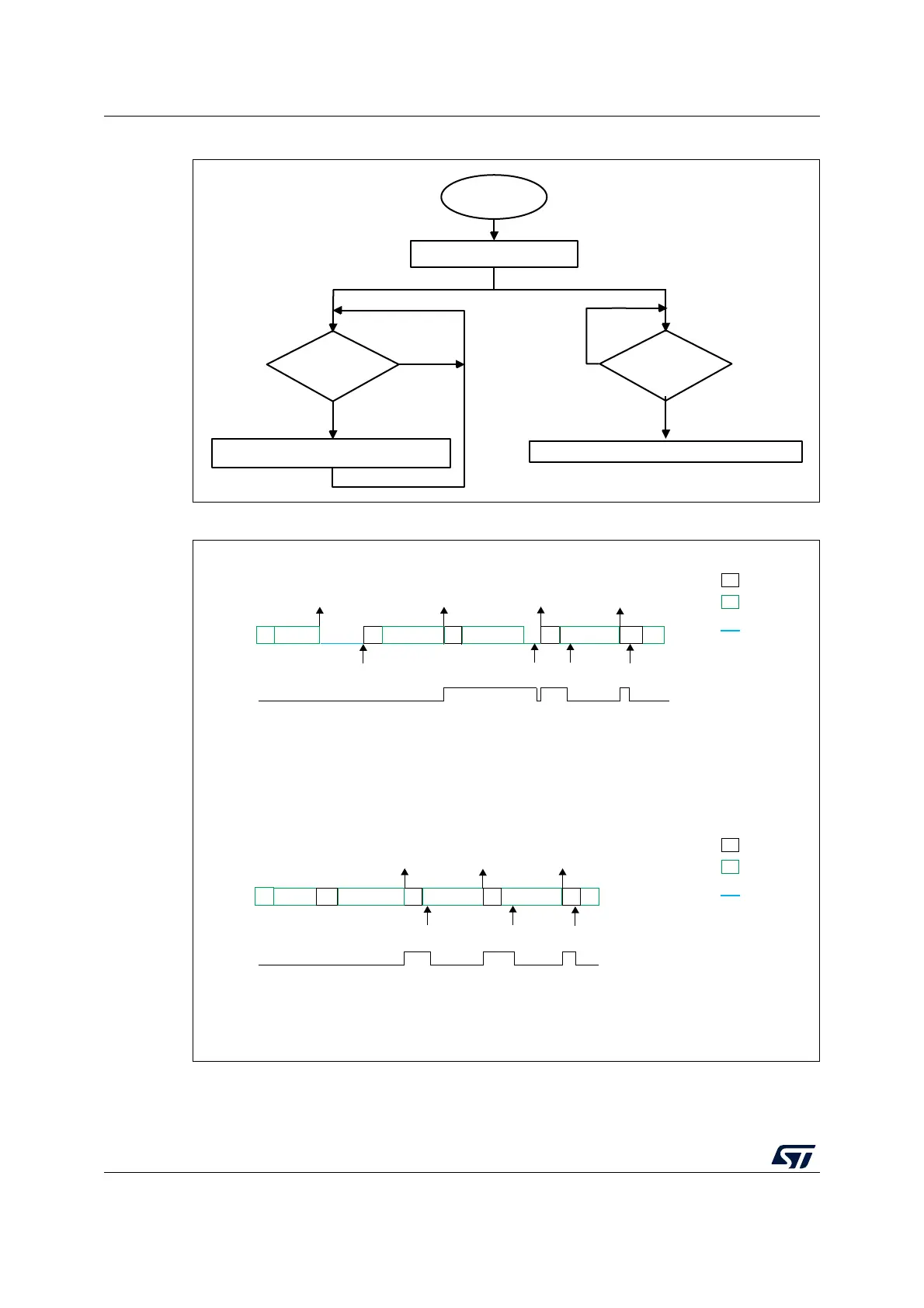

Figure 220. Transfer bus diagrams for FMPI2C slave receiver

MS35978V1

EV1: ADDR ISR: check ADDCODE and DIR, set ADDRCF

EV2: RXNE ISR: rd data1

EV3 : RXNE ISR: rd data2

EV4: RXNE ISR: rd data3

A

ADDR

AA

RXNE

A

RXNE

RXNE

legend:

transmission

reception

SCL stretch

EV1 EV2 EV3

EV1: RXNE ISR: rd data1

EV2: RXNE ISR: rd data2

EV3: RXNE ISR: rd data3

EV4: STOPF ISR: set STOPCF

A

AA A

RXNE

legend:

transmission

reception

SCL stretch

RXNE

EV4

Example FMPI2C slave receiver 3 bytes, NOSTRETCH=1:

S

Address data 1 data 2 data 3

P

Example FMPI2C slave receiver 3 bytes, NOSTRETCH=0:

S

Address data1 data2 data3

EV3

EV2

EV1

RXNE RXNE RXNE

Loading...

Loading...