Fast-mode Plus Inter-integrated circuit (FMPI2C) interface RM0402

666/1163 RM0402 Rev 6

23.4.7 Data transfer

The data transfer is managed through transmit and receive data registers and a shift

register.

Reception

The SDA input fills the shift register. After the 8th SCL pulse (when the complete data byte is

received), the shift register is copied into FMPI2C_RXDR register if it is empty (RXNE=0). If

RXNE=1, meaning that the previous received data byte has not yet been read, the SCL line

is stretched low until FMPI2C_RXDR is read. The stretch is inserted between the 8th and

9th SCL pulse (before the acknowledge pulse).

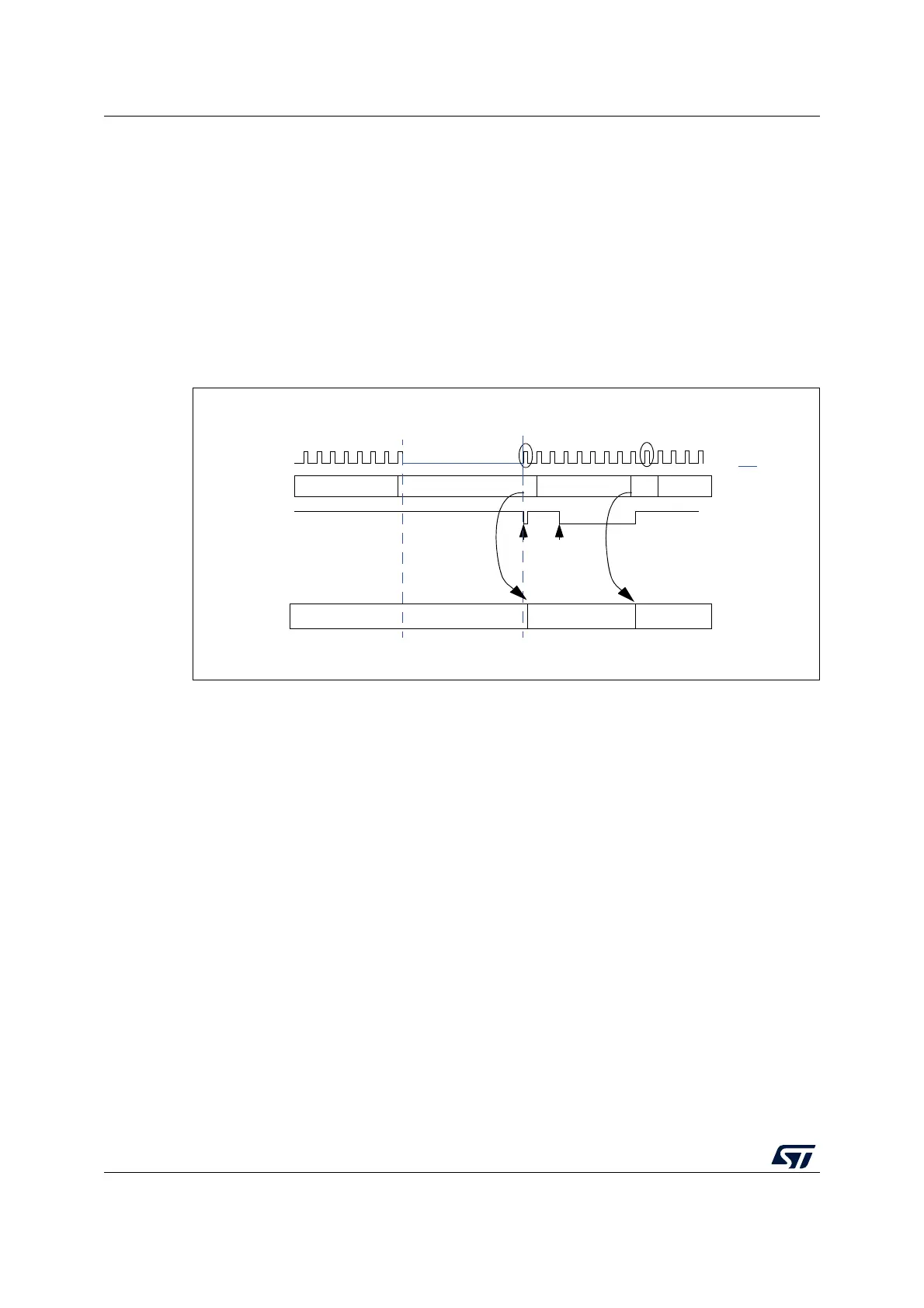

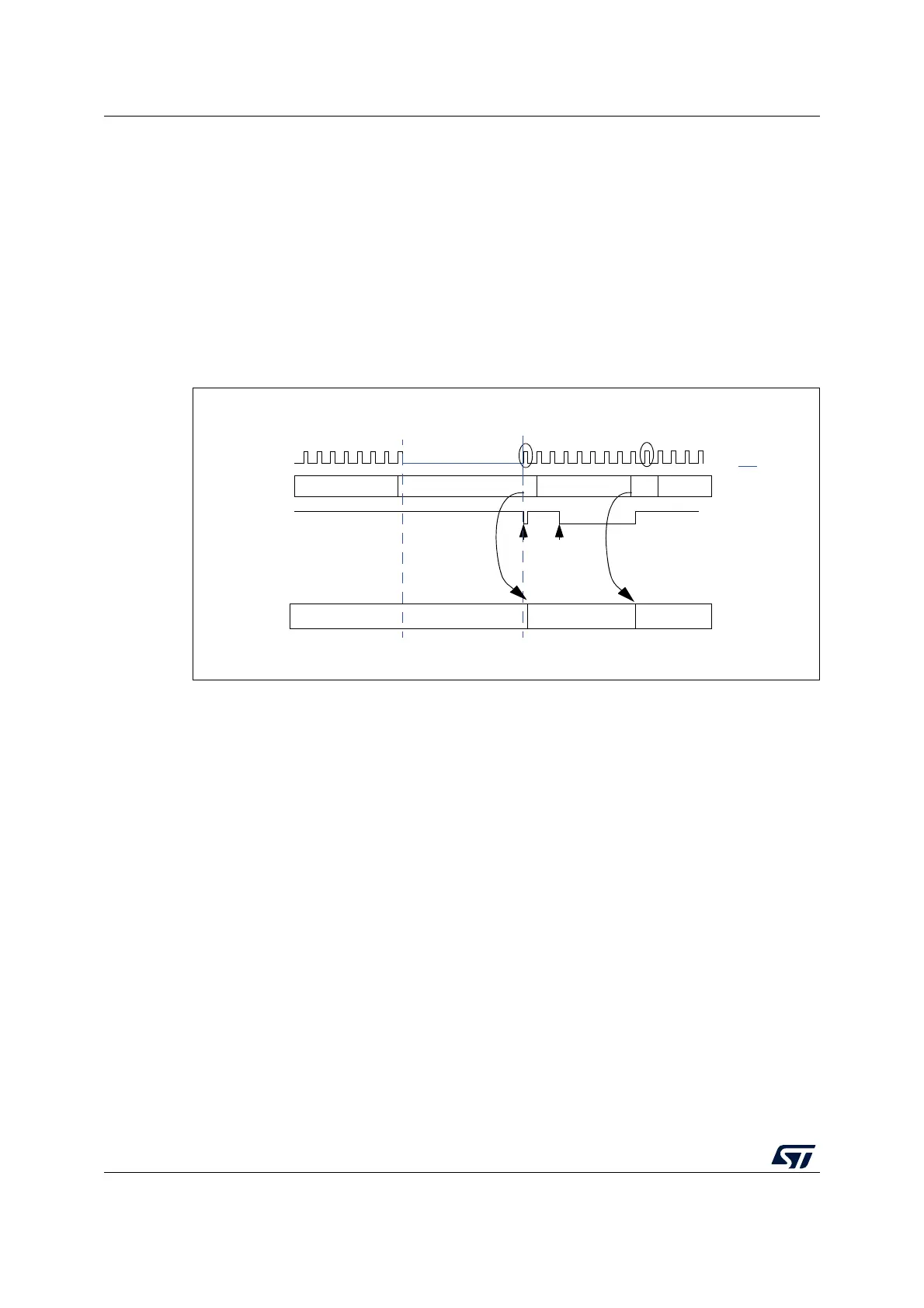

Figure 212. Data reception

xx

Shift register

data1

data1

xx data2

RXNE

ACK pulse

data0 data2

ACK pulse

xx

FMPI2C_RXDR

rd data1rd data0

SCL

legend:

SCL

stretch

MSv35976V1

Loading...

Loading...