Reset and clock control (RCC) for STM32F412xx RM0402

140/1163 RM0402 Rev 6

6.3.11 RCC AHB2 peripheral clock enable register (RCC_AHB2ENR)

Address offset: 0x34

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access.

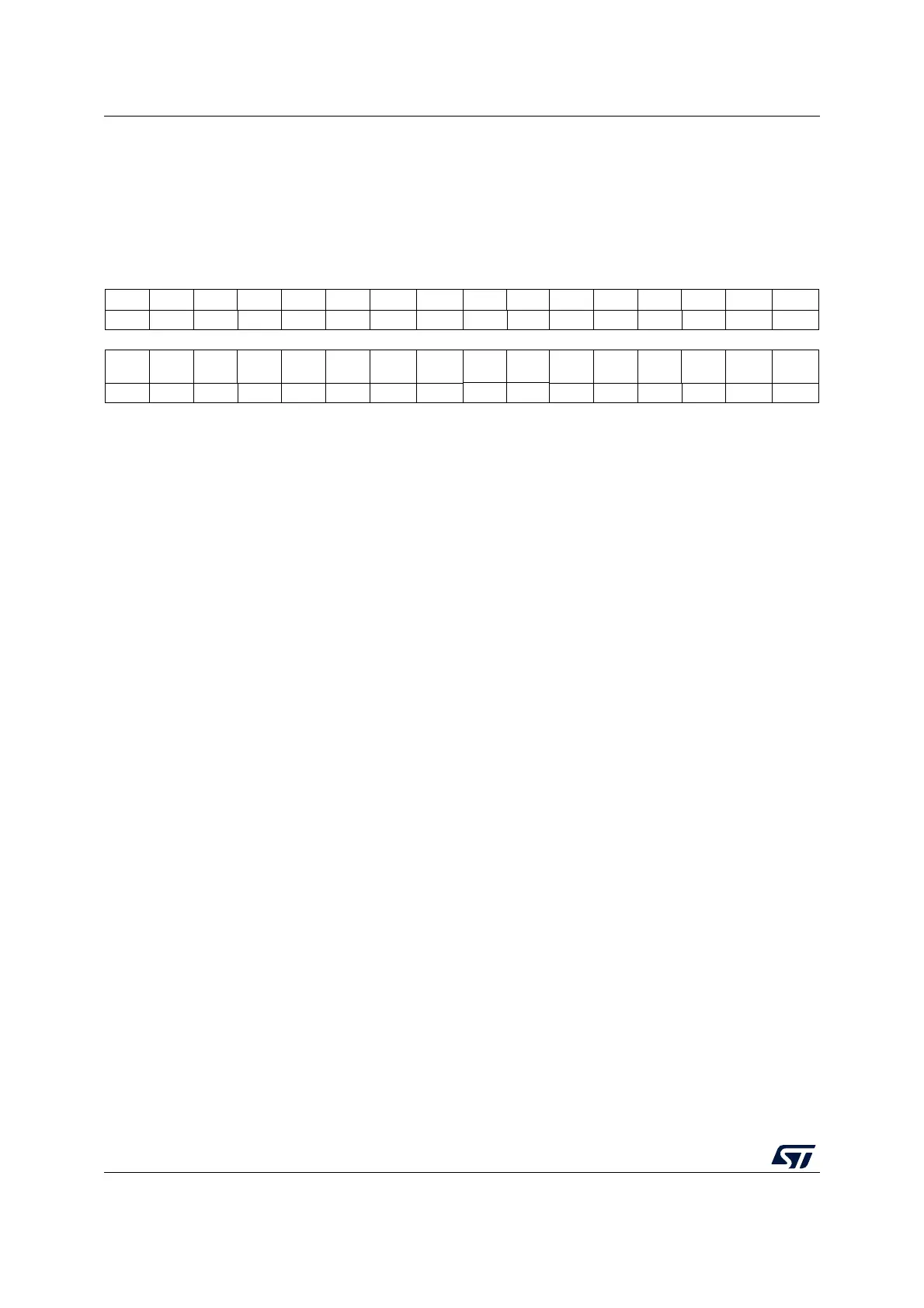

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res.

OTGFS

EN

RNG

EN

Res. Res. Res. Res. Res. Res.

rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bit 7 OTGFSEN: USB OTG FS clock enable

Set and cleared by software.

0: USB OTG FS clock disabled

1: USB OTG FS clock enabled

Bit 6 RNGEN: RNG clock enable

Set and cleared by software.

0: RNG clock disabled

1: RNG clock enabled

Bits 5:0 Reserved, always read as 0.

Loading...

Loading...