Inter-integrated circuit (I

2

C) interface RM0402

746/1163 RM0402 Rev 6

Note: When the STOP, START or PEC bit is set, the software must not perform any write access

to I2C_CR1 before this bit is cleared by hardware. Otherwise there is a risk of setting a

second STOP, START or PEC request.

24.6.2 I

2

C control register 2 (I2C_CR2)

Address offset: 0x04

Reset value: 0x0000

Bit 2 Reserved, must be kept at reset value

Bit 1 SMBUS: SMBus mode

0: I

2

C mode

1: SMBus mode

Bit 0 PE: Peripheral enable

0: Peripheral disable

1: Peripheral enable

Note: If this bit is reset while a communication is on going, the peripheral is disabled at the

end of the current communication, when back to IDLE state.

All bit resets due to PE=0 occur at the end of the communication.

In master mode, this bit must not be reset before the end of the communication.

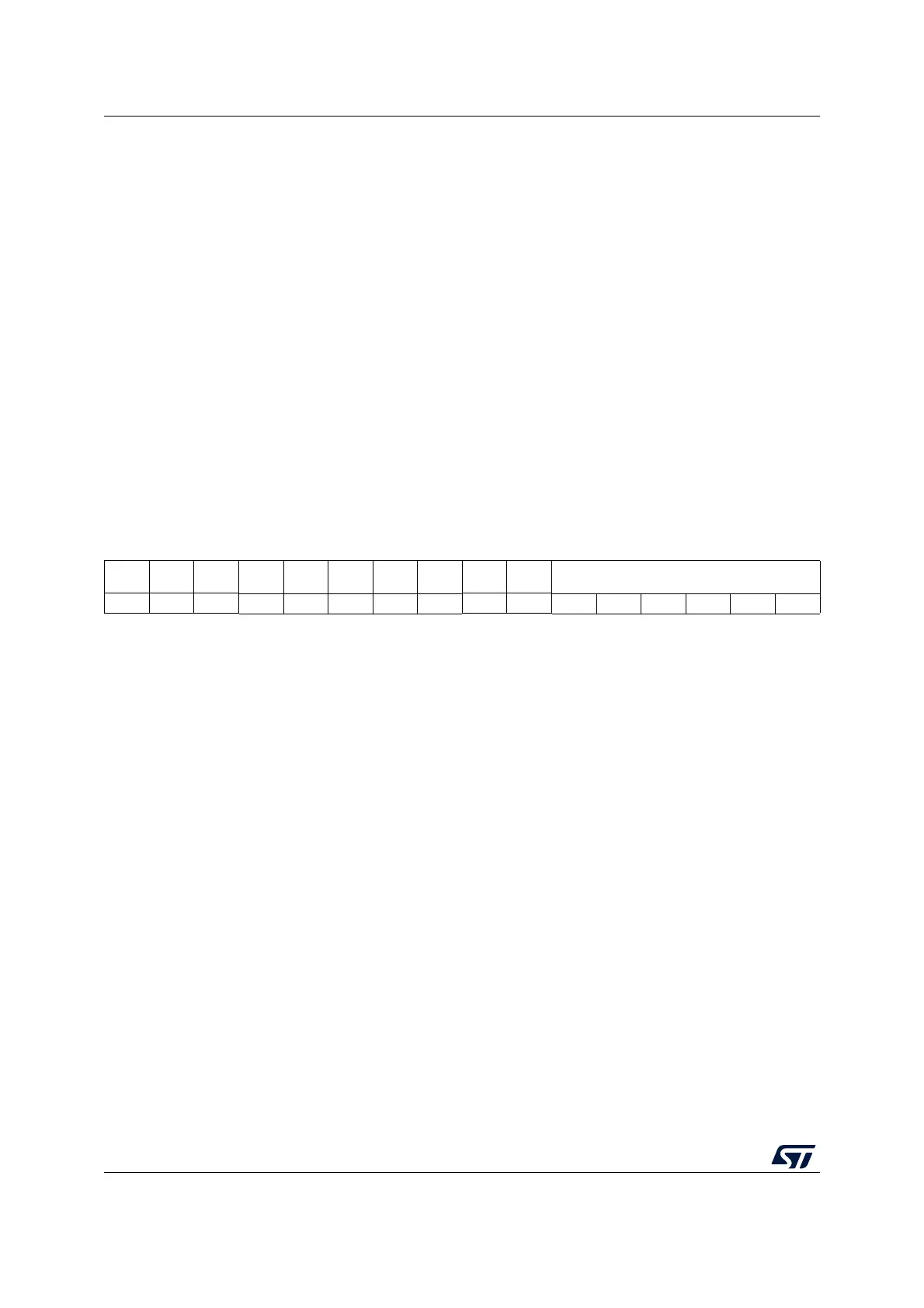

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. LAST

DMA

EN

ITBUF

EN

ITEVT

EN

ITERR

EN

Res. Res. FREQ[5:0]

rw rw rw rw rw rw rw rw rw rw rw

Bits 15:13 Reserved, must be kept at reset value

Bit 12 LAST: DMA last transfer

0: Next DMA EOT is not the last transfer

1: Next DMA EOT is the last transfer

Note: This bit is used in master receiver mode to permit the generation of a NACK on the last

received data.

Bit 11 DMAEN: DMA requests enable

0: DMA requests disabled

1: DMA request enabled when TxE=1 or RxNE =1

Bit 10 ITBUFEN: Buffer interrupt enable

0: TxE = 1 or RxNE = 1 does not generate any interrupt.

1: TxE = 1 or RxNE = 1 generates Event Interrupt (whatever the state of DMAEN)

Bit 9 ITEVTEN: Event interrupt enable

0: Event interrupt disabled

1: Event interrupt enabled

This interrupt is generated when:

– SB = 1 (Master)

– ADDR = 1 (Master/Slave)

– ADD10= 1 (Master)

– STOPF = 1 (Slave)

– BTF = 1 with no TxE or RxNE event

– TxE event to 1 if ITBUFEN = 1

– RxNE event to 1if ITBUFEN = 1

Loading...

Loading...