System configuration controller (SYSCFG) RM0402

192/1163 RM0402 Rev 6

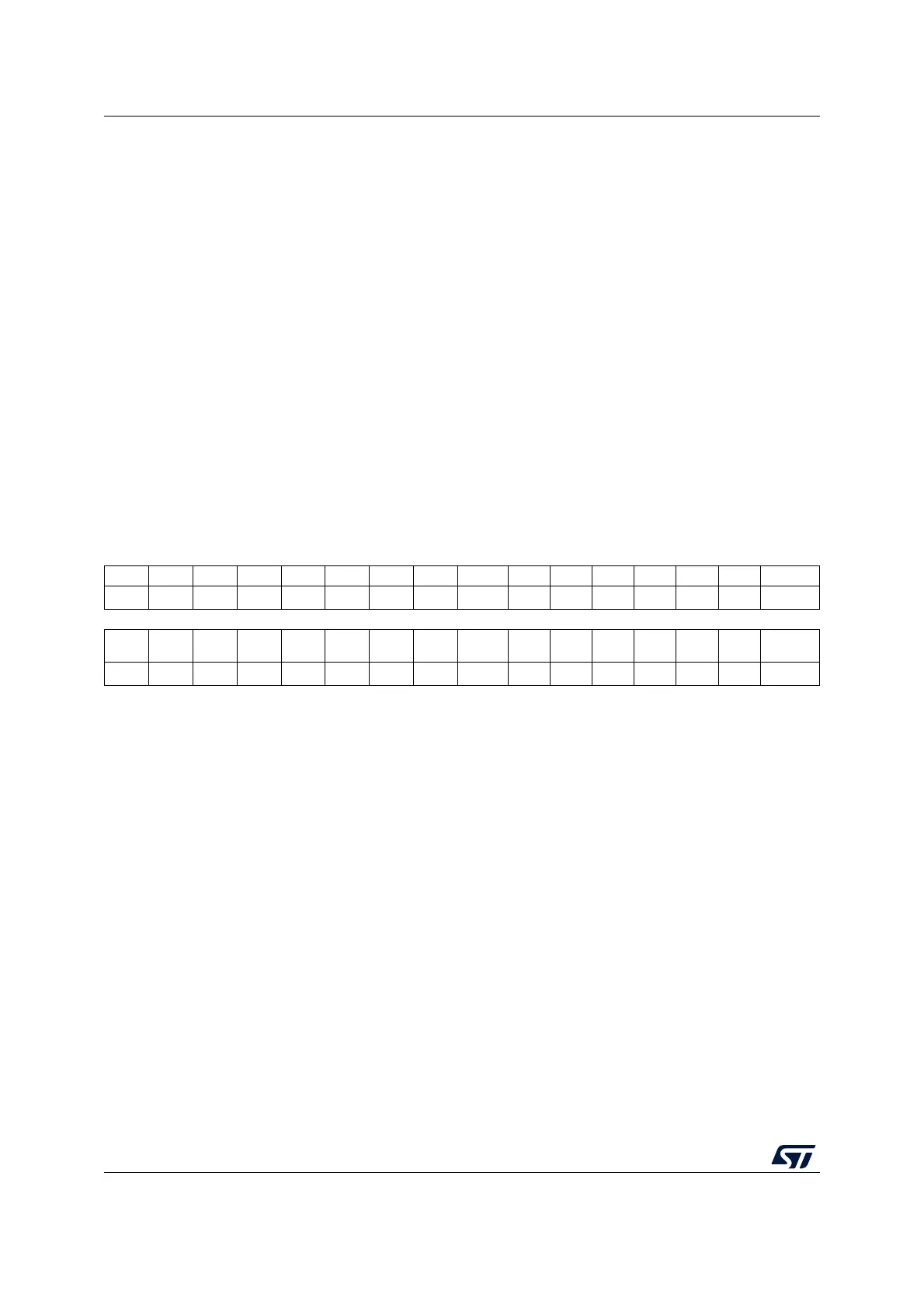

8.2.8 Compensation cell control register (SYSCFG_CMPCR)

Address offset: 0x20

Reset value: 0x0000 0000

Bit 2 PVDL: PVD lock

This bit is set by software. It can be cleared only by a system reset. It enables and

locks the PVD connection to TIM1/8 Break input. It also locks (write protection) the

PVDE and PVDS[2:0] bits of PWR_CR register.

0: PVD interrupt not connected to TIM1/8 Break input. PVDE and PVDS[2:0] can be

read and modified

1: PVD interrupt connected to TIM1/8 Break input. PVDE and PVDS[2:0] are read-

only

Bit 1 Reserved, must be kept at reset value.

Bit 0 CLL: core lockup lock

This bit is set and cleared by software. It enables and locks the LOCKUP (Hardfault)

output of the Cortex

®

-M4 with FPU core with TIM1/8 Break input.

0: Cortex

®

-M4 with FPU LOCKUP output not connected to TIM1/8 Break input

1: Cortex

®

-M4 with FPU LOCKUP output connected to TIM1/8 Break input

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 7 654321 0

Res. Res. Res. Res. Res. Res. Res. READY Res. Res. Res. Res. Res. Res. Res. CMP_PD

r rw

Bits 31:9 Reserved, must be kept at reset value.

Bit 8 READY: Compensation cell ready flag

0: I/O compensation cell not ready

1: O compensation cell ready

Bits 7:2 Reserved, must be kept at reset value.

Bit 0 CMP_PD: Compensation cell power-down

0: I/O compensation cell power-down mode

1: I/O compensation cell enabled

Loading...

Loading...