Direct memory access controller (DMA) RM0402

224/1163 RM0402 Rev 6

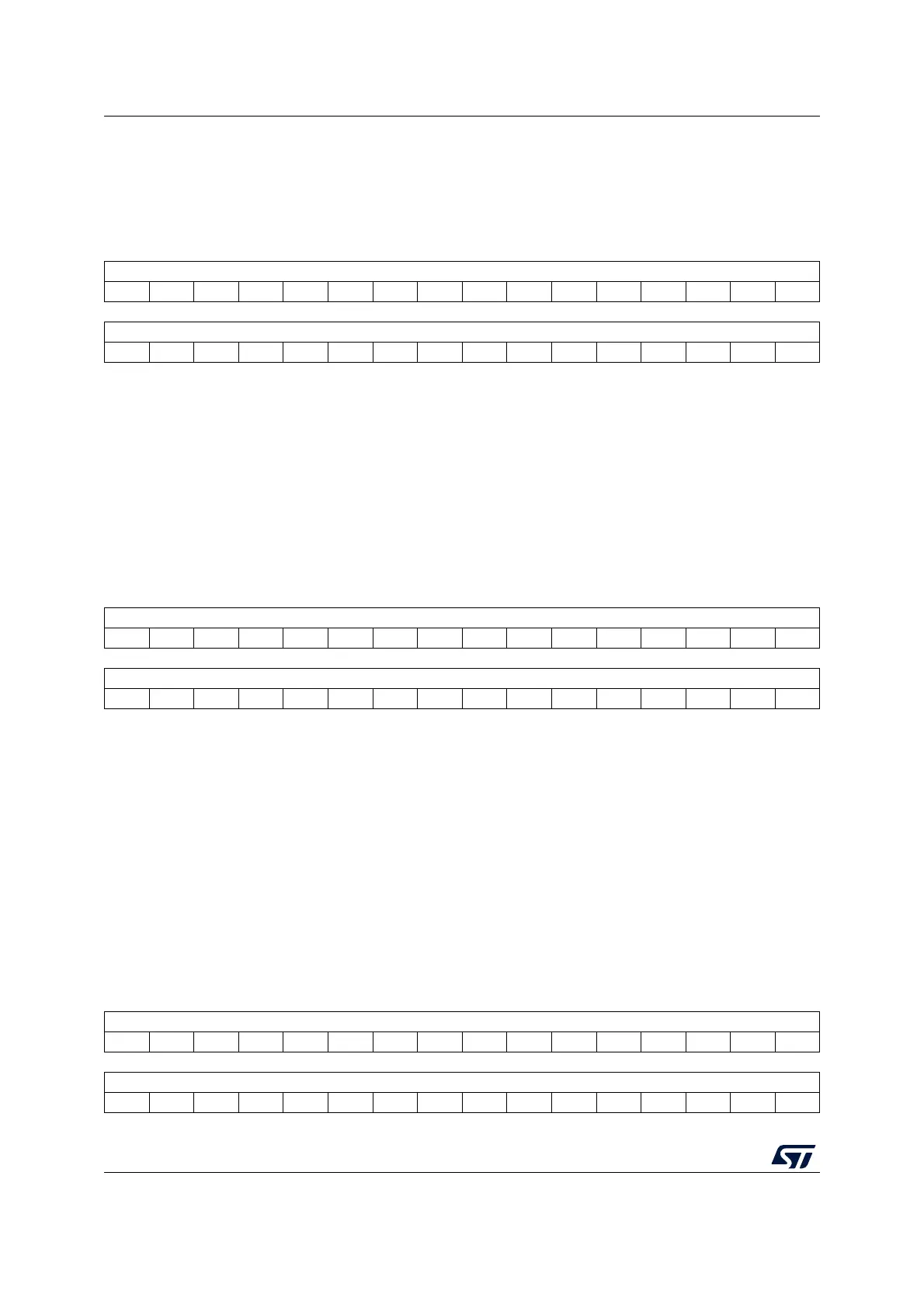

9.5.7 DMA stream x peripheral address register (DMA_SxPAR)

Address offset: 0x018 + 0x018 * x, (x = 0 to 7)

Reset value: 0x0000 0000

9.5.8 DMA stream x memory 0 address register

(DMA_SxM0AR)

Address offset: 0x01C + 0x018 * x, (x = 0 to 7)

Reset value: 0x0000 0000

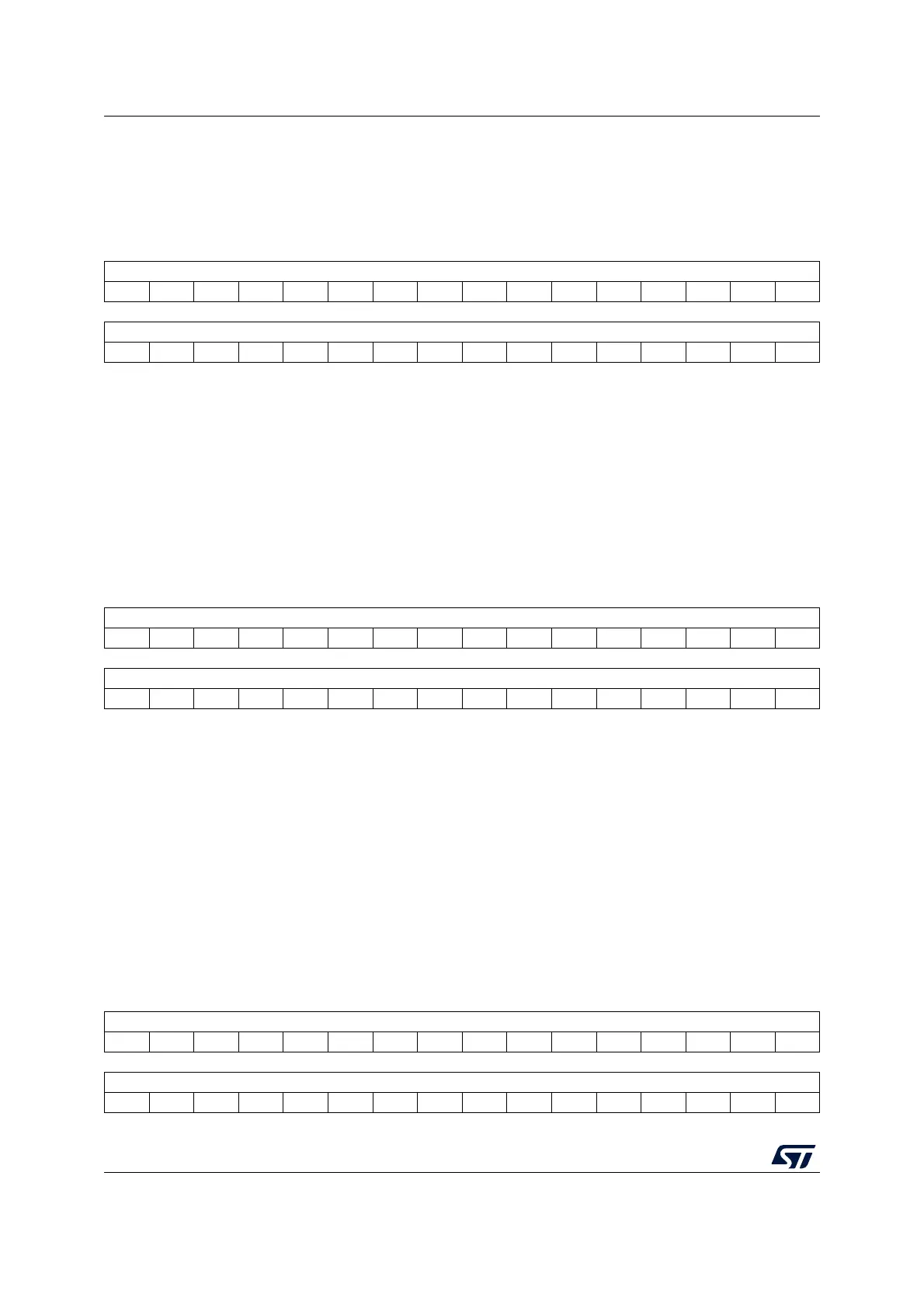

9.5.9 DMA stream x memory 1 address register

(DMA_SxM1AR)

Address offset: 0x020 + 0x018 * x, (x = 0 to 7)

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PAR[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

PAR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 PAR[31:0]: peripheral address

Base address of the peripheral data register from/to which the data is read/written.

These bits are write-protected and can be written only when bit EN = 0 in DMA_SxCR.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

M0A[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

M0A[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 M0A[31:0]: memory 0 address

Base address of memory area 0 from/to which the data is read/written.

These bits are write-protected. They can be written only if:

– the stream is disabled (EN = 0 in DMA_SxCR) or

– the stream is enabled (EN = 1 in DMA_SxCR) and CT = 1 in DMA_SxCR (in

double-buffer mode).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

M1A[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

M1A[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...