RM0402 Rev 6 313/1163

RM0402 Quad-SPI interface (QUADSPI)

316

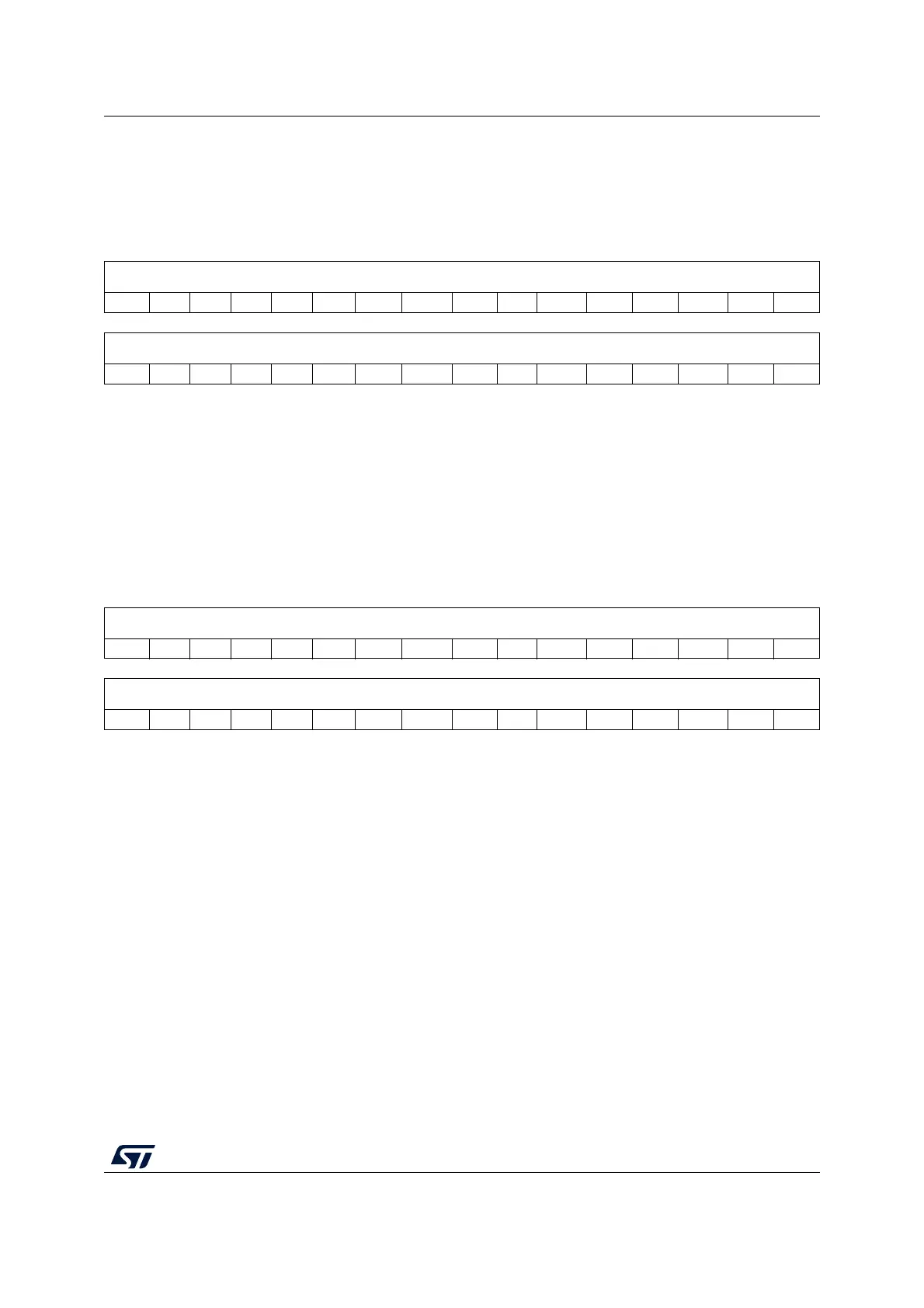

12.5.8 QUADSPI alternate bytes registers (QUADSPI_ABR)

Address offset: 0x001C

Reset value: 0x0000 0000

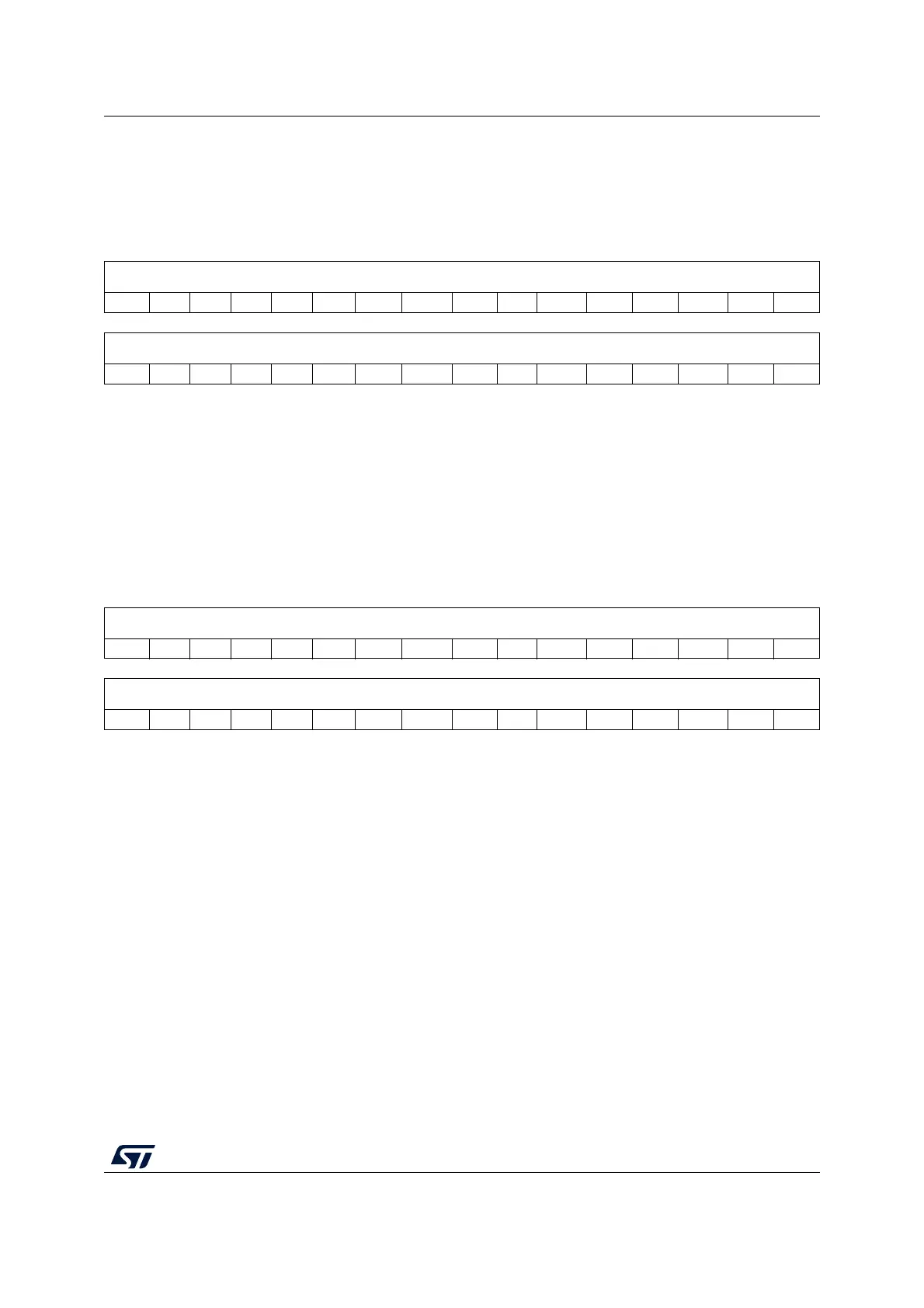

12.5.9 QUADSPI data register (QUADSPI_DR)

Address offset: 0x0020

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ALTERNATE[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ALTERNATE[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 ALTERNATE[31:0]: Alternate Bytes

Optional data to be send to the external SPI device right after the address.

This field can be written only when BUSY = 0.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DATA[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DATA[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 DATA[31:0]: Data

Data to be sent/received to/from the external SPI device.

In indirect write mode, data written to this register is stored on the FIFO before it is sent

to the Flash memory during the data phase. If the FIFO is too full, a write operation is

stalled until the FIFO has enough space to accept the amount of data being written.

In indirect read mode, reading this register gives (via the FIFO) the data which was

received from the Flash memory. If the FIFO does not have as many bytes as requested

by the read operation and if BUSY=1, the read operation is stalled until enough data is

present or until the transfer is complete, whichever happens first.

In automatic polling mode, this register contains the last data read from the Flash

memory (without masking).

Word, halfword, and byte accesses to this register are supported. In indirect write mode,

a byte write adds 1 byte to the FIFO, a halfword write 2, and a word write 4. Similarly, in

indirect read mode, a byte read removes 1 byte from the FIFO, a halfword read 2, and a

word read 4. Accesses in indirect mode must be aligned to the bottom of this register: a

byte read must read DATA[7:0] and a halfword read must read DATA[15:0].

Loading...

Loading...